Министерство науки и высшего образования

Российской Федерации

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

**А.А. Жигальский**

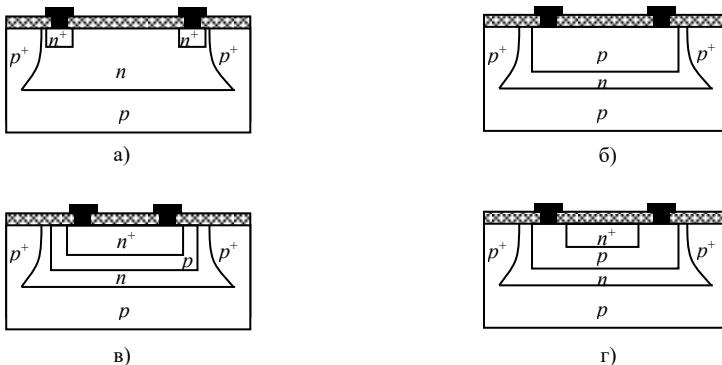

**ПРОЕКТИРОВАНИЕ ЭЛЕКТРОННОЙ КОМПОНЕНТНОЙ

БАЗЫ МИКРОЭЛЕКТРОНИКИ И

МИКРОСИСТЕМНОЙ ТЕХНИКИ**

Учебное пособие

**Томск

2025**

УДК 621.382.049.77.002(075.8)

ББК 32.844я73

Ж68

**Рецензент:**

**Троян Павел Ефимович,**

доктор технических наук, профессор кафедры физическая

электроника ФГАОУ ВО «Томский государственный

университет систем управления и радиоэлектроники»

**Жигальский, Александр Анатольевич**

Ж68 Проектирование электронной компонентной базы

микроэлектроники и микросистемной техники: Учебное

пособие / А.А. Жигальский. - Томск: Томск. гос. ун-т систем

упр. и радиоэлектроники, 2025. – 204 с.

Приведен лекционный курс по дисциплине «Проектирование

электронной компонентной базы микроэлектроники и микросистемной

техники». В пособии рассматриваются вопросы проектирования

гибридных микросхем, полупроводниковых микросхем на биполярных

и МДП-транзисторах, базовых марочных кристаллов, элементов

постоянных запоминающих устройств.

Предназначено для студентов высших учебных заведений

технических специальностей.

**УДК 621.382.049.77.002(075.8)**

**ББК 32.844я73**

Одобрено на заседании кафедры физической

электроники протокол №162 от 07.11.2024 года

© Жигальский А.А., 2025

© Томск. гос. ун-т систем упр. и

радиоэлектроники, 2025

## СОДЕРЖАНИЕ

|                                                                                 |     |

|---------------------------------------------------------------------------------|-----|

| ВВЕДЕНИЕ .....                                                                  | 5   |

| 1 ИЗДЕЛИЯ МИКРОЭЛЕКТРОНИКИ .....                                                | 6   |

| 2 КОНСТРУИРОВАНИЕ И РАСЧЕТ ГИБРИДНЫХ<br>МИКРОСХЕМ .....                         | 11  |

| 2.1 Подложки .....                                                              | 11  |

| 2.2 Материалы пленок тонкопленочных микросхем .....                             | 14  |

| 2.3 Расчет конструкций тонкопленочных резисторов .....                          | 26  |

| 2.4 Тонкопленочные конденсаторы .....                                           | 35  |

| 2.5 Пленочные индуктивности .....                                               | 41  |

| 2.6 Конструкции тонкопленочных распределенных<br>RC-структур .....              | 44  |

| 2.7 Особенности конструкций СВЧ ГИС .....                                       | 46  |

| 2.8 Конструкции компонентов гибридных микросхем .....                           | 50  |

| 2.9 Проектирование топологии гибридных ИМС .....                                | 59  |

| 3 ТОЛСТОПЛЕНОЧНЫЕ ГИС .....                                                     | 66  |

| 3.1 Платы толстопленочных ГИС .....                                             | 66  |

| 3.2 Пасты для толстопленочных ГИС .....                                         | 67  |

| 3.3 Основные технологические операции изготовления<br>толстопленочных ГИС ..... | 68  |

| 4 КОНТРОЛЬНО-ПРОВЕРОЧНЫЕ РАСЧЕТЫ .....                                          | 71  |

| 4.1 Паразитные связи в гибридных ИМС .....                                      | 71  |

| 4.2 Обеспечение тепловых режимов работы ИМС .....                               | 73  |

| 5 ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ НА БИПОЛЯРНЫХ<br>ТРАНЗИСТОРАХ .....                   | 79  |

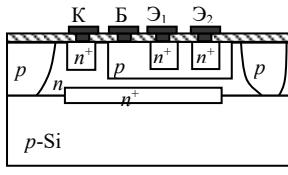

| 5.1 Подложки полупроводниковых интегральных<br>микросхем .....                  | 79  |

| 5.2 Конструирование и выбор структуры интегральных<br>транзисторов .....        | 84  |

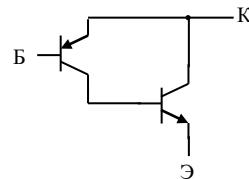

| 5.3 Конструирование и расчет диодов .....                                       | 96  |

| 5.4 Интегральные резисторы .....                                                | 102 |

| 5.5 Конструирование и расчет конденсаторов .....                                | 112 |

| 5.6 Диоды и транзисторы с барьером Шоттки .....                                 | 115 |

| 5.7 Методы изоляции элементов ИМС .....                                         | 118 |

| 5.8 Разработка топологии полупроводниковых ИМС .....                            | 125 |

|                                                                                                 |            |

|-------------------------------------------------------------------------------------------------|------------|

| 5.9 Тепловой режим полупроводниковых ИМС .....                                                  | 135        |

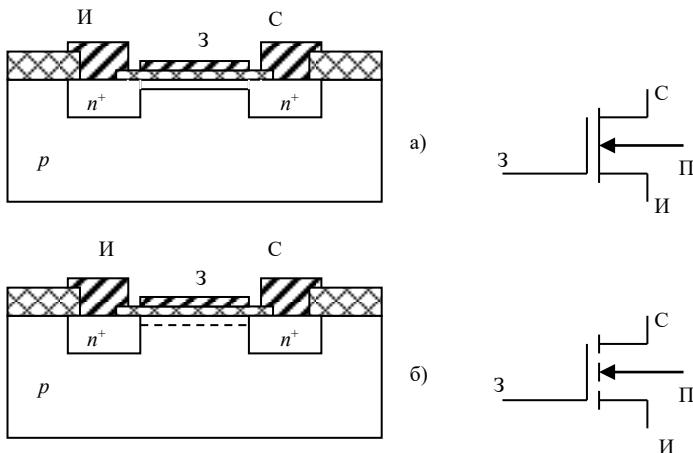

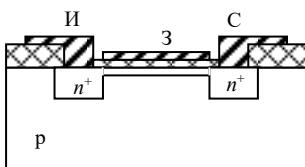

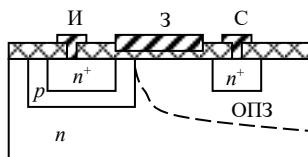

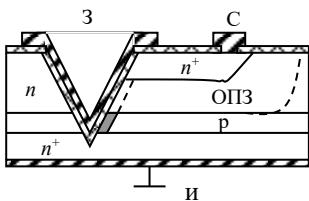

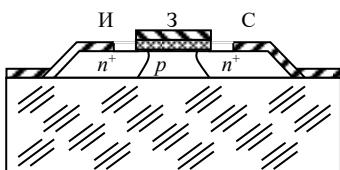

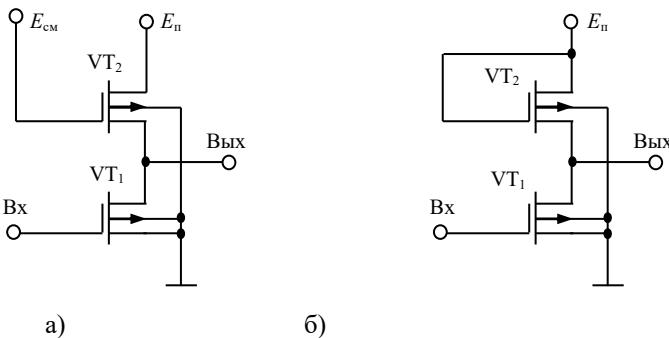

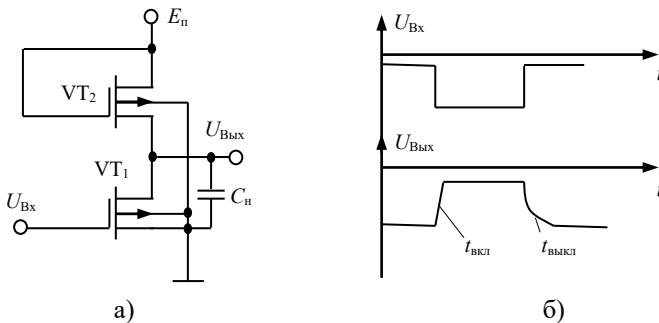

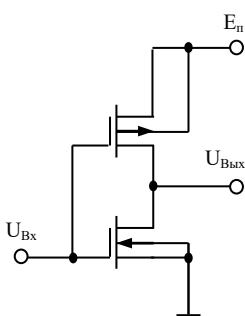

| <b>6 ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ НА<br/>МДП-ТРАНЗИСТОРАХ.....</b>                                   | <b>139</b> |

| 6.1 Типы МДП-транзисторов .....                                                                 | 139        |

| 6.2 Основные принципы построения МДП ИМС .....                                                  | 148        |

| 6.3 Проектирование топологии МДП ИМС .....                                                      | 156        |

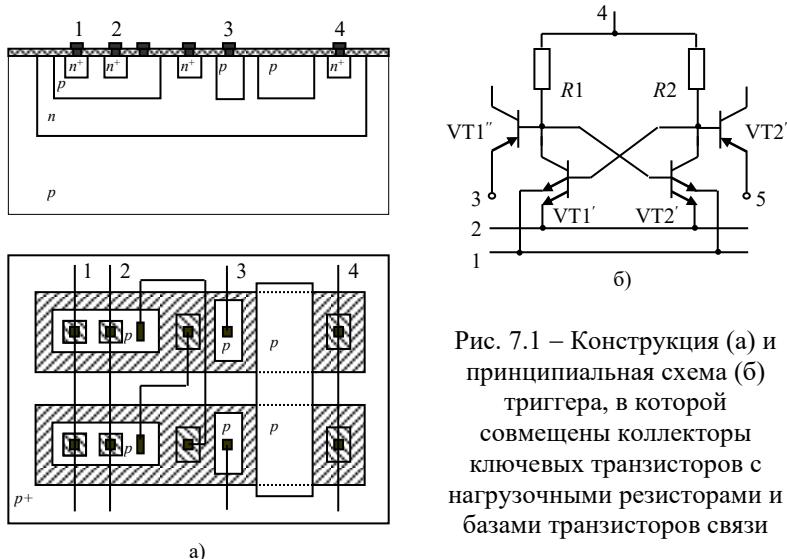

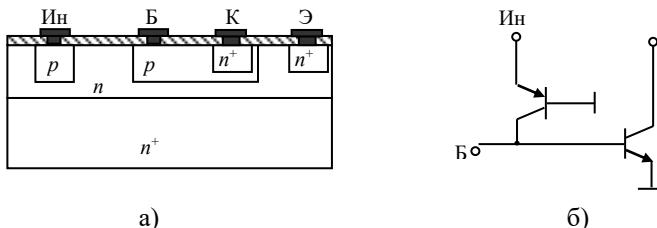

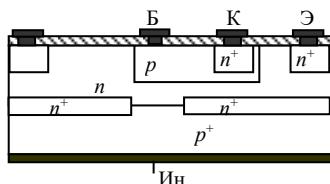

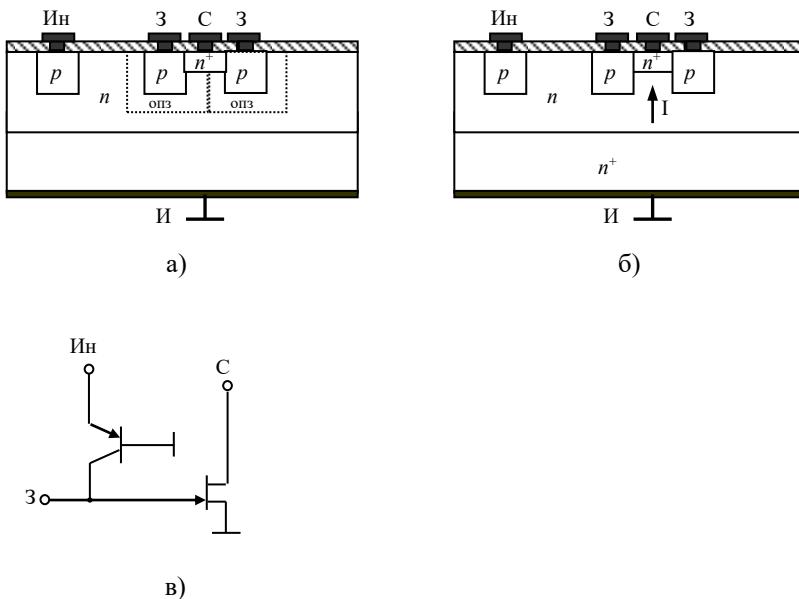

| <b>7 МИКРОСХЕМЫ С ФУНКЦИОНАЛЬНО-<br/>ИНТЕГРИРОВАННЫМИ ЭЛЕМЕНТАМИ .....</b>                      | <b>162</b> |

| <b>8 ЭЛЕМЕНТЫ ПОЛУПРОВОДНИКОВЫХ ПОСТОЯННЫХ<br/>ЗАПОМИНАЮЩИХ УСТРОЙСТВ .....</b>                 | <b>168</b> |

| <b>9 БАЗОВЫЕ МАТРИЧНЫЕ КРИСТАЛЛЫ .....</b>                                                      | <b>179</b> |

| 9.1 Принципы построения базовых матричных кристаллов. ....                                      | 179        |

| 9.2 Базовые матричные кристаллы на основе<br>биполярных транзисторов .....                      | 184        |

| 9.3 Базовые матричные кристаллы на основе полевых<br>транзисторов с изолированным затвором..... | 188        |

| 9.4 Проектирование микросхем на основе базовых<br>матричных кристаллов.....                     | 190        |

| <b>10 КОНСТРУКТИВНОЕ ОФОРМЛЕНИЕ И ЗАЩИТА<br/>МИКРОСХЕМ .....</b>                                | <b>192</b> |

| 10.1 Корпуса микросхем .....                                                                    | 192        |

| 10.2 Защита поверхности кристалла бескорпусных<br>микросхем .....                               | 201        |

| <b>ЛИТЕРАТУРА .....</b>                                                                         | <b>203</b> |

## **ВВЕДЕНИЕ**

Данное учебное пособие предназначено для самостоятельного изучения курса «Проектирование электронной компонентной базы микроэлектроники и микросистемной техники» студентами специальностей, связанных с разработкой интегральных устройств твердотельной электроники и содержит основные разделы изучаемой дисциплины. В пособии рассматриваются вопросы проектирования гибридных микросхем, полупроводниковых микросхем на биполярных и МДП-транзисторах, базовых матричных кристаллов, элементов постоянных запоминающих устройств. При разработке учебного пособия ставилась задача достаточно полного и доступного изложения материала. Здесь содержатся данные, необходимые для выполнения студентами курсового проекта по разработке топологии интегральной микросхемы.

Для успешного изучение курса необходимо также знание основ полупроводниковой технологии и принципов работы полупроводниковых приборов.

## 1 ИЗДЕЛИЯ МИКРОЭЛЕКТРОНИКИ

Интегральная микросхема (ИМС) – это конструктивно законченное микроэлектронное изделие, выполняющее определенную функцию преобразования информации, содержащее совокупность электрически связанных между собой элементов (транзисторов, диодов, резисторов и др.), изготовленных в едином технологическом цикле. Термин «интегральная микросхема» отражает суммирование, объединение значительного числа элементов и соединяющих их проводников в единую конструкцию (конструктивная интеграция), выполнение функций преобразования более сложных по сравнению с функциями отдельных дискретных приборов (схемотехническая интеграция), создание одновременно всех элементов и межэлементных соединений в едином технологическом цикле (технологическая интеграция). Микросхемы изготавливают групповым методом по материалосберегающей технологии, тиражируя одновременно в одной партии от нескольких десятков до нескольких десятков тысяч микросхем.

По конструктивно-технологическому исполнению микросхемы делят на три группы: полупроводниковые, пленочные и гибридные.

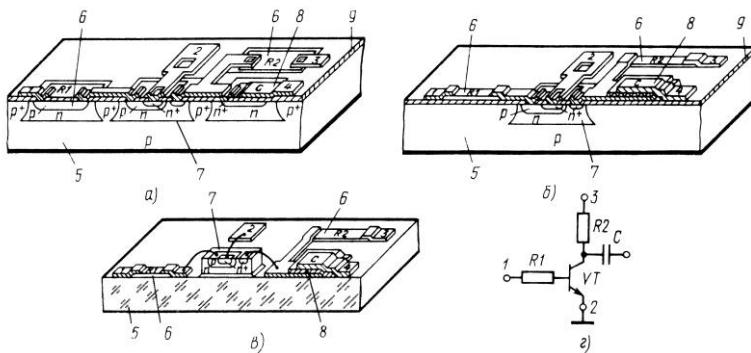

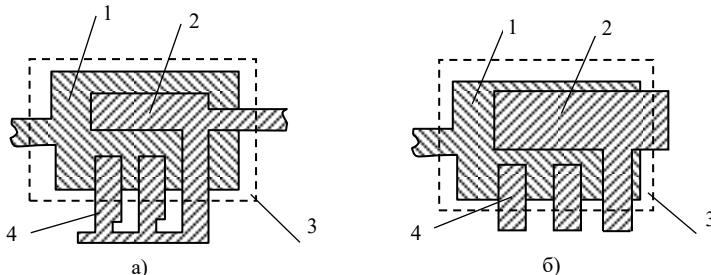

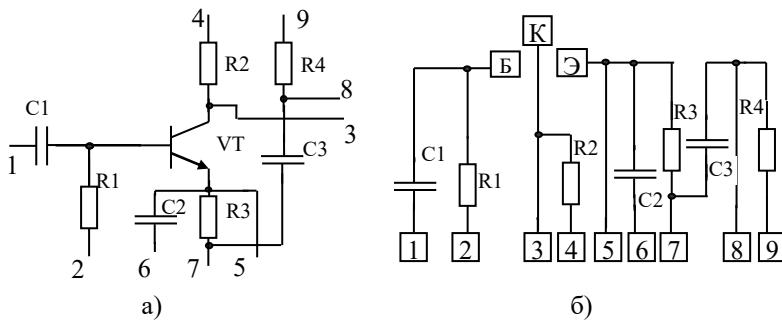

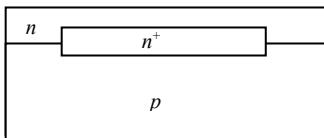

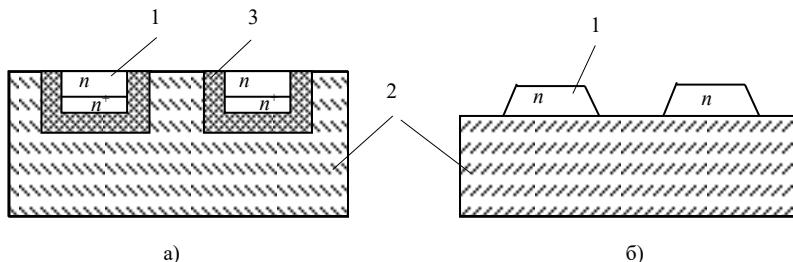

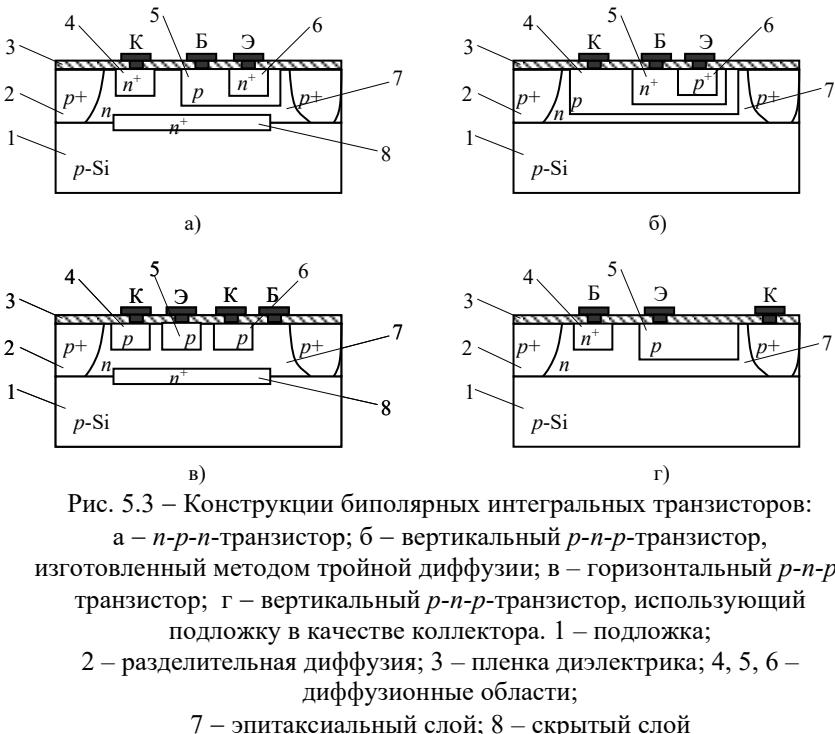

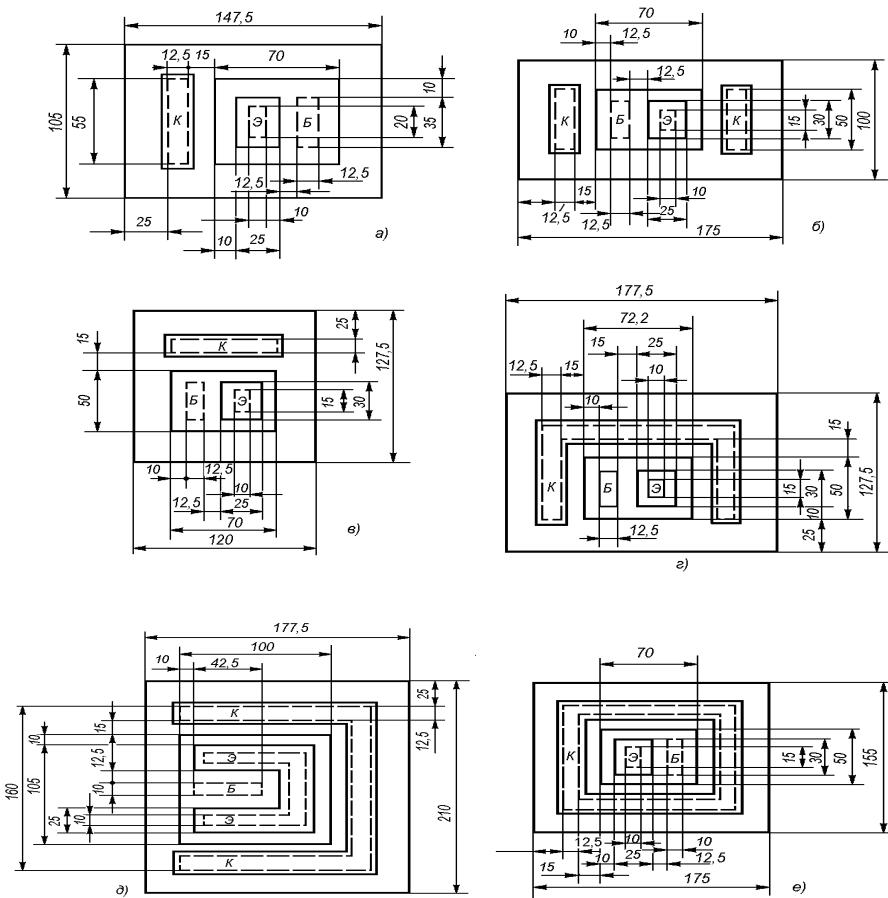

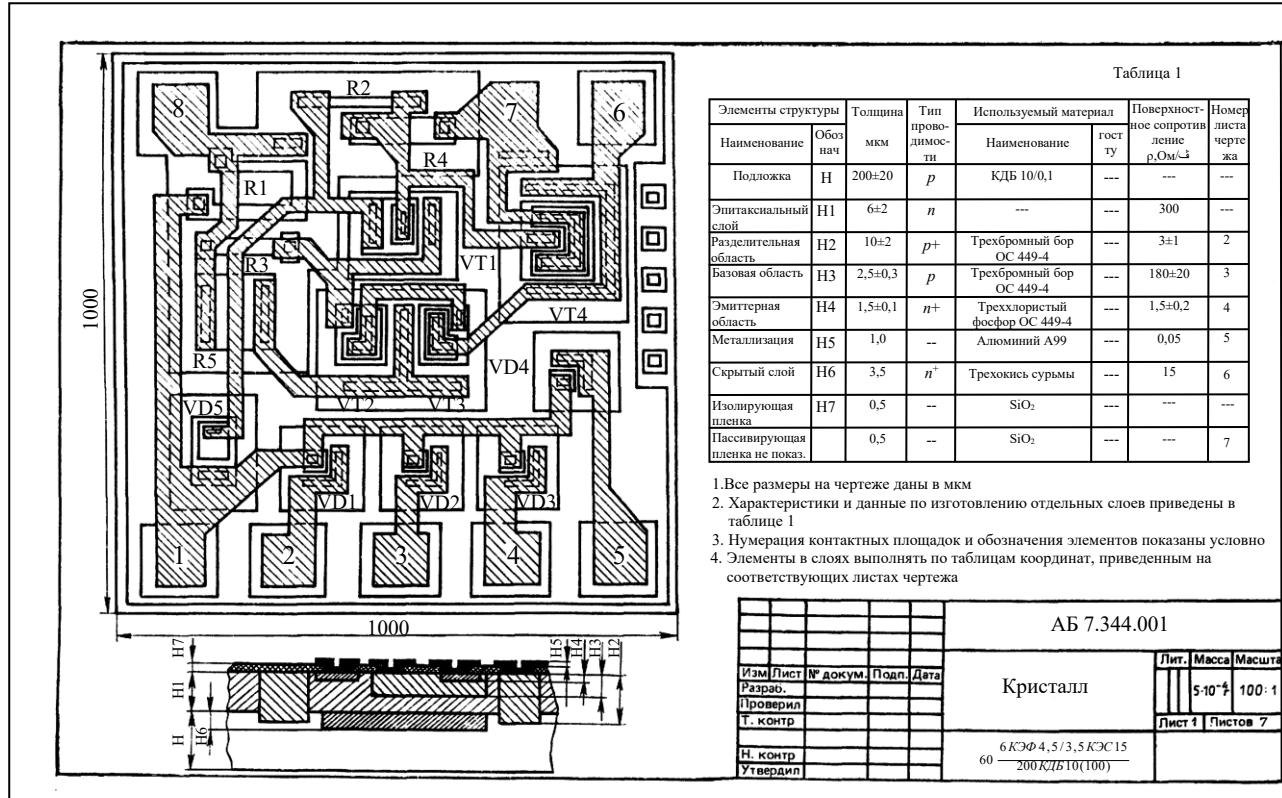

В *полупроводниковой* интегральной микросхеме все элементы и межэлементные соединения выполнены в объеме и на поверхности полупроводниковой подложки. На рис. 1.1 *a, б* показаны два варианта изготовления фрагмента полупроводниковой интегральной схемы (ИС), содержащего транзистор, два резистора и конденсатор. В первом варианте транзистор, оба резистора и одна из обкладок конденсатора сформированы в полупроводниковой подложке. Во втором варианте все пассивные элементы выполнены по тонкопленочной, а транзистор по полупроводниковой технологии.

Элемент интегральной микросхемы – это ее неотделимая составная часть, выполняющая какую-либо функцию. Поэтому транзисторы, диоды, конденсаторы, резисторы микросхемы

называют *интегральными*, в отличие от отдельно изготавляемых транзисторов, диодов, конденсаторов, резисторов, которые в этом случае называют *дискретными*.

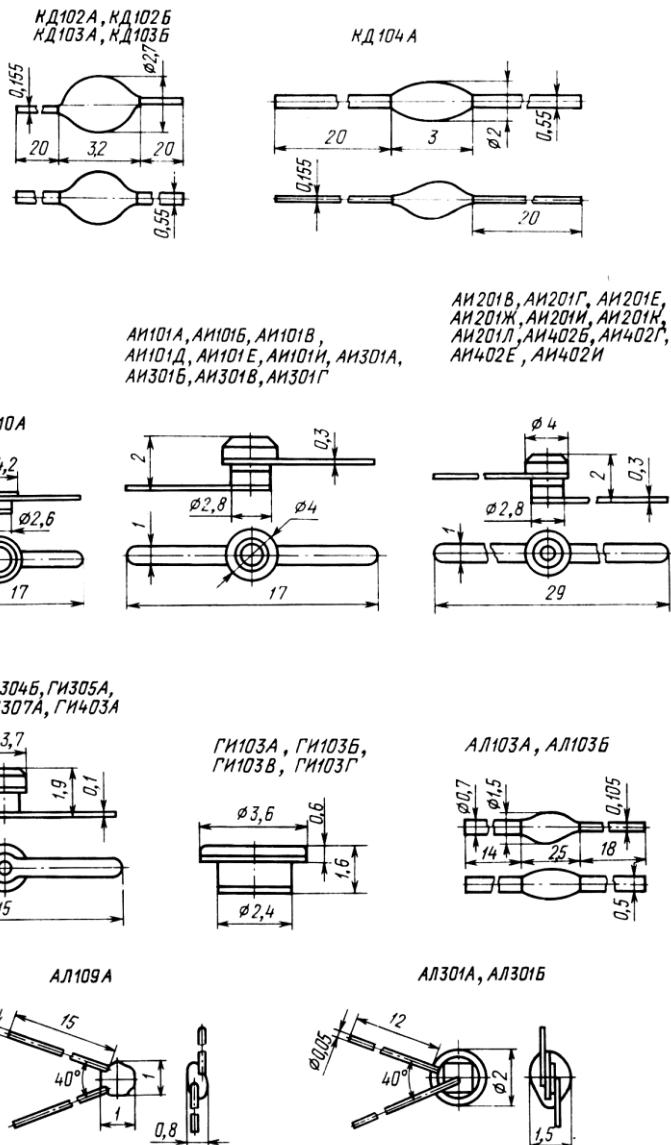

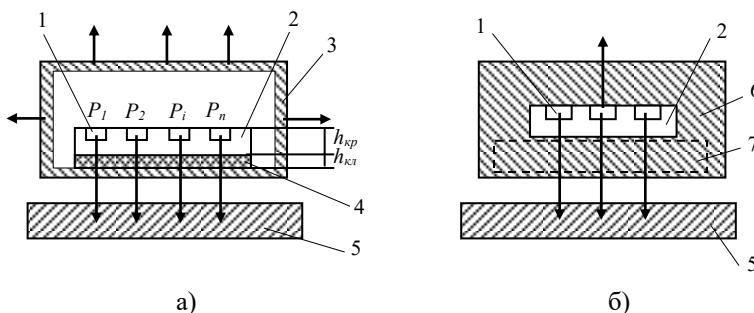

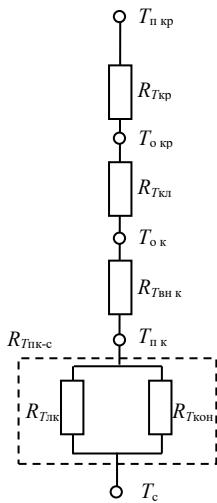

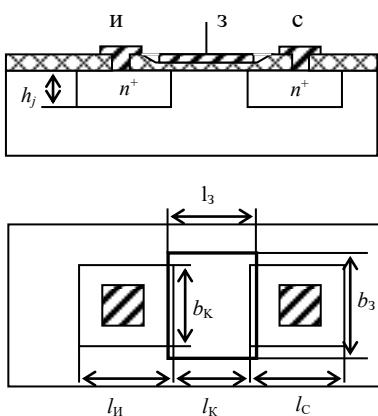

Рис. 1.1 – Варианты конструктивно-технологического исполнения интегральных микросхем: а – полупроводниковая; б – совмещенная; в – гибридная; г – схема электрическая принципиальная; 1-4 – выводы и контактные площадки; 5 – подложка; 6 – резисторы; 7 – транзисторы; 8 – конденсаторы; 9 – пленка

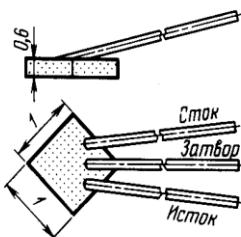

По типу используемых основных активных элементов полупроводниковые микросхемы подразделяют на биполярные и полевые (на МДП-транзисторах). Выпускаются также комбинированные биполярно-полевые полупроводниковые микросхемы, в которых, наряду с биполярными, используются и полевые транзисторы с *p-n*-переходом, характеризующиеся высоким входным сопротивлением и низким уровнем шумов.

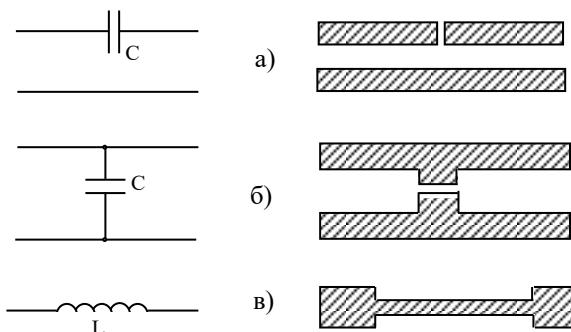

В *пленочной интегральной микросхеме* все элементы и соединения между ними выполнены в виде пленок. В настоящее время методами пленочной технологии реализуются только пассивные элементы микросхем – резисторы, конденсаторы и индуктивности.

В зависимости от толщины пленок и способа создания элементов микросхемы подразделяют на *тонкопленочные* и *толстопленочные*. К первым относят микросхемы, толщина пленок в которых не превышает 1 мкм. (Проводящая

металлическая пленка называется тонкой, если ее толщина меньше длины свободного пробега в ней электронов.) Тонкопленочные элементы формируют различными методами: термического испарения материалов в вакууме, электрохимического осаждения из газовой фазы.

В *совмещенных микросхемах* все активные элементы и часть пассивных изготавливают по полупроводниковой технологии в пластине кремния, а часть пассивных элементов – по тонкопленочной технологии. Пассивные элементы располагают на гладких поверхностях защитного диэлектрика, не содержащих ступенек. Необходимость создания совмещенных микросхем вызвана тем, что тонкопленочные резисторы по сравнению с полупроводниковыми обладают более высокими номиналами сопротивлений и точностью изготовления, меньшими величинами паразитных параметров, низким термическим коэффициентом сопротивления, а тонкопленочные конденсаторы, в отличие от полупроводниковых, могут работать при любой полярности. При производстве совмещенных микросхем приходится вводить дополнительные операции нанесения тонких пленок и принимать дополнительные меры защиты тонкопленочных резисторов.

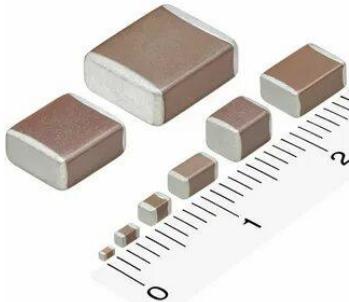

В *гибридной микросхеме* в качестве активных элементов используются навесные дискретные полупроводниковые приборы или полупроводниковые интегральные микросхемы, а в качестве пассивных элементов – пленочные резисторы, конденсаторы, катушки индуктивности и соединяющие их пленочные проводники. Механической основой такой микросхемы является диэлектрическая подложка. Довольно часто в составе гибридной микросхемы используют не только пленочные, но и миниатюрные дискретные конденсаторы, резисторы, катушки индуктивности, дроссели, трансформаторы. Их называют навесными компонентами. Этим подчеркивается, что они изготавливаются отдельно и представляют собой самостоятельные изделия, которые могут приобретаться изготовителем гибридных микросхем как покупные изделия.

Частью конструкции микросхемы является ее подложка. Она выполняет функции: механического основания, изоляции элементов друг от друга, теплоотвода. Подложки выпускаются в виде тонких круглых или прямоугольных пластин. Для полупроводниковых микросхем используют монокристаллические полупроводниковые (кремний, арсенид галлия) и монокристаллические диэлектрические (сапфир, шпинель) подложки. На последних в дальнейшем формируют слой полупроводникового материала, в котором создают элементы микросхем. Их круглая форма определяется способом получения монокристаллических слитков методом вытягивания их из расплава. Для тонкопленочных и гибридных микросхем используют подложки из стекла, стеклокристаллического материала (ситалла) и керамики.

Часть подложки, отведенную под одну микросхему, отделенную от других частей вместе со сформированными на ней элементами, в полупроводниковой технологии называют кристаллом, а в пленочной технологии – *платой*.

В настоящее время микросхемы выпускают в корпусном и бескорпусном исполнениях. Корпуса герметичны и защищают микросхемы от воздействия окружающей среды. Бескорпусные микросхемы предназначены для работы в составе радиоэлектронных устройств, которые целиком размещаются в герметизируемых объемах. Их покрывают лаком или заливают компаундами для защиты от внешних воздействий.

По функциональному назначению микросхемы подразделяются на *цифровые и аналоговые*. Если микросхема предназначена для преобразования и обработки сигналов, изменяющихся по закону дискретной функции, то она называется цифровой (логической). К аналоговым относятся микросхемы, предназначенные для преобразования и обработки сигнала, изменяющегося линейно.

Показателем сложности микросхемы является *степень интеграции K*, которая характеризуется числом содержащихся в ней элементов и компонентов  $N:K=\lg N$ , где  $K$  округляется до ближайшего большего целого числа.

Наибольшей степенью интеграции обладают полупроводниковые микросхемы, затем тонкопленочные и, наконец, толстопленочные (в том числе, гибридные). По степени интеграции полупроводниковые микросхемы на биполярных транзисторах уступают интегральным микросхемам на МДП-транзисторах.

Микросхемы выпускаются в виде серий, к которым относится ряд типов микросхем с различным функциональным назначением, имеющих единое конструктивно-технологическое исполнение и предназначенных для совместного использования. Каждый тип микросхем имеет свое условное обозначение. Система условных обозначений (маркировка) микросхем, выпускаемых отечественными предприятиями для устройств широкого применения, состоит из шести элементов.

Например: КР1118ПА1Б

1 2 3 4 5 6

1 – элемент показывает, что микросхема предназначена для устройств широкого применения;

2 – характеристика материала и типа корпуса:

Е – металлополимерный корпус;

Р – пластмассовый корпус с двухрядным расположением выводов;

М – металлокерамический или керамический корпус;

С – стеклокерамический корпус;

Б – бескорпусные микросхемы;

3 – элемент (одна цифра) указывает группу микросхемы по конструктивно-технологическому признаку:

1, 5, 6, 7 – полупроводниковые;

2, 4, 8 – гибридные;

3 – прочие;

4 – элемент (две или три цифры) определяет порядковый номер разработки серии;

5 – элемент (две буквы) определяет функциональное назначение схемы;

6 – порядковый номер разработки внутри серии. Следующие затем буквы от А до Я указывают допуск на разброс по электрическим параметрам.

## **2 КОНСТРУИРОВАНИЕ И РАСЧЕТ ГИБРИДНЫХ МИКРОСХЕМ**

### **2.1 Подложки**

Гибридные микросхемы находят широкое применение в современной электронике. Эти микросхемы обладают рядом достоинств, среди которых можно отметить возможность использования разнообразных активных элементов, что позволяет создавать микросхемы с широким диапазоном выполняемых функций. Кроме того, элементы гибридных ИМС обладают высокой температурной и временной стабильностью. Основными конструктивными элементами гибридных микросхем являются: диэлектрическая подложка; пленочные резисторы, конденсаторы, индуктивности, проводники, контактные площадки; навесные полупроводниковые приборы (транзисторы, диоды, микросхемы), навесные пассивные элементы (конденсаторы с большой емкостью, трансформаторы, дроссели и т.д.).

Подложка выполняет роль основания, на поверхности которого формируются по заданному рисунку пленочные элементы микросхемы. К конструкции и материалу подложки предъявляется ряд требований, вытекающих из необходимости обеспечения заданных электрических параметров микросхемы, ее надежности и особенностей технологии изготовления пассивных элементов. Материал подложки должен обладать:

- высоким сопротивлением изоляции, низкой диэлектрической проницаемостью и низким тангенсом угла диэлектрических потерь, высокой электрической прочностью для обеспечения качественной электрической изоляции элементов микросхемы, как на постоянном токе, так и в широком диапазоне частот;

- высокой механической прочностью, обеспечивающей целостность подложки с нанесенными элементами как в процессе изготовления микросхемы (разделение на субподложки, термокомпрессия, пайка, установка подложки в корпус и т.д.), так и при ее эксплуатации в условиях термоциклирования, термоударов и механических воздействий;

- высокой химической инертностью к осаждаемым материалам для снижения временной нестабильности параметров пленочных элементов, обусловленной физико-химическими процессами на границе раздела пленка-подложка и проникновением ионов из подложки в пленку;

- стойкостью к воздействию высокой температуры в процессе нанесения тонких пленок и термообработки паст при формировании стеклоэмалевых пленок;

- стойкостью к воздействию химических реагентов в процессе подготовки поверхности подложки перед нанесением пленок, при электрохимических обработках и химическом осаждении пленок;

- способностью к хорошей механической обработке (полировке, резке).

Материалы подложки и нанесенных на нее пленок должны иметь незначительно различающиеся температурные коэффициенты линейного расширения (ТКЛР) для обеспечения достаточно малых механических напряжений в пленках, вызывающих их отслаивание и растрескивание при охлаждении подложки после нанесения пленочных элементов. Кроме того, подложки тонкопленочных ИС должны обладать малым газовыделением для устранения атмосферы в камере напылительной установки.

Структура материала подложки и состояние ее поверхности оказывают существенное влияние на структуру выращиваемых тонких пленок и характеристики пленочных элементов. Большая шероховатость поверхности подложки снижает надежность тонкопленочных резисторов и конденсаторов, так как микронеровности уменьшают толщину резистивных и диэлектрических пленок. При толщине пленок около 100 нм допускается высота микронеровностей примерно 25 нм. Следовательно, обработка поверхности подложки для тонкопленочных микросхем должна соответствовать 14 классу чистоты. Толстые пленки имеют толщину 10...50 мкм, поэтому подложки для толстопленочных ИС могут иметь микронеровности до 1 мкм, что соответствует 8...10 классам

чистоты. Для обеспечения хорошей адгезии пасты к подложке высота микронеровностей должна быть 50÷200 нм.

Таблица 2.1 – Типоразмеры плат ГИС

| № типо-размера | Ширина | Ширина | № типо-размера | Ширина | Длина |

|----------------|--------|--------|----------------|--------|-------|

| 1              | 96     | 120    | 11             | 5      | 6     |

| 2              | 60     | 96     | 12             | 2,5    | 4     |

| 3              | 48     | 60     | 13             | 16     | 60    |

| 4              | 30     | 48     | 14             | 32     | 60    |

| 5              | 24     | 30     | 15             | 8      | 15    |

|                |        |        |                |        |       |

| 6              | 20     | 24     | 16             | 8      | 10    |

| 7              | 16     | 20     | 17             | 24     | 60    |

| 8              | 12     | 16     | 18             | 15     | 48    |

| 9              | 10     | 16     | 19             | 20     | 45    |

| 10             | 10     | 12     |                |        |       |

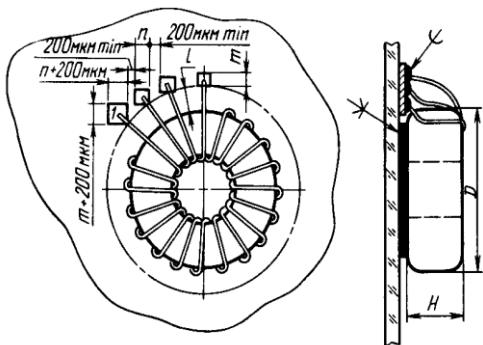

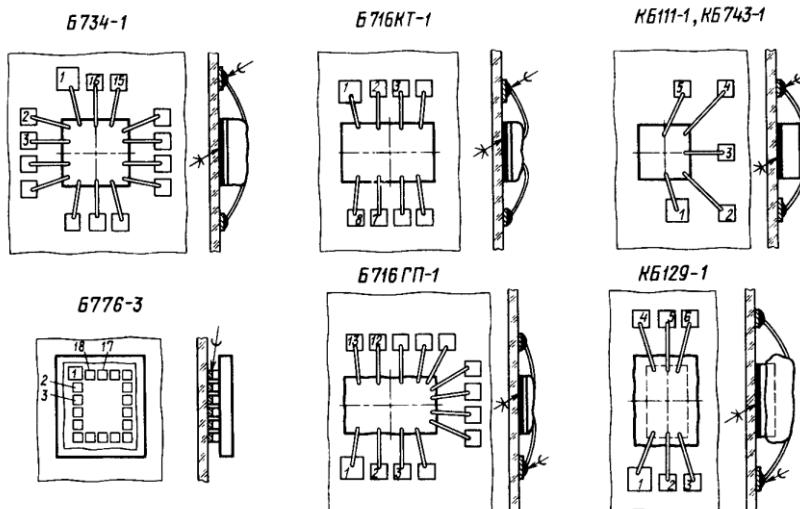

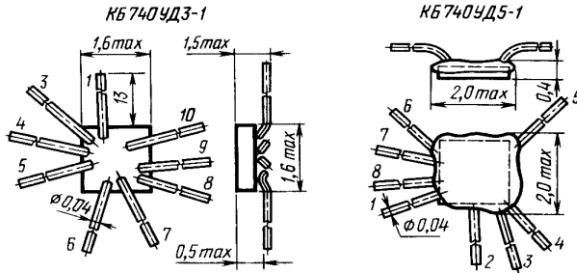

Габаритные размеры подложек стандартизованы. Обычно на стандартной подложке групповым методом изготавливаются несколько плат пленочных микросхем. Безотходное деление стандартной подложки на 2, 3, 4, 6, 8, 12 и более частей дает нормализованный ряд типоразмеров плат. Рекомендуемые к применению типоразмеры плат даны в табл. 2.1. Размеры плат № 3–10 соответствуют посадочным местам стандартных корпусов. Платы с остальными номерами применяются в микросборках. Толщина подложек составляет 0,35...0,6 мм.

Для изготовления подложек применяются бесщелочные стекла, ситалл и керамика. Электрофизические характеристики ситалла удовлетворяют большинству требований, предъявляемых к материалам подложек, поэтому ситалл нашел наибольшее применение в производстве маломощных тонкопленочных ГИС. Основным недостатком ситалла является низкая теплопроводность.

Керамические подложки используются при изготовлении микросхем повышенной мощности благодаря высокому коэффициенту теплопроводности. Наибольшей тепло-

проводностью обладает бериллиевая керамика (99,5% BeO). В производстве тонкопленочных ИС керамические подложки предварительно покрывают тонким слоем окиси tantalа или бесщелочного стекла (стеклянная глазурь) для получения гладкой поверхности. В толстопленочных ИС в основном применяют высокоглиноземистые керамики 22ХС (96%  $Al_2O_3$ ) и «Поликор», характеризующиеся высокой температурой размягчения, так как обжиг высокотемпературных пироэмалей, применяемых при формировании толстопленочных элементов, производится при температурах около 900°C. Основные характеристики материалов подложек представлены в табл. 2.2.

## 2.2 Материалы пленок тонкопленочных микросхем

Основными элементами тонкопленочных микросхем являются резисторы и конденсаторы. Тонкопленочные индуктивности применяются значительно реже из-за сложности их изготовления.

*Материалы тонкопленочных резисторов.* К ним, в первую очередь, предъявляются определенные требования по поверхностному сопротивлению. Наибольшее распространение имеют резисторы с сопротивлениями от 10 Ом до 10 МОм. Линейные размеры резисторов приходится ограничивать: максимальную длину из-за ограниченности размеров подложек, а минимальные длину и ширину – из соображений допустимого разброса. Если ограничить ширину и минимальную длину резистора размером 0,1 мм, а максимальную длину – размером 10 мм, то диапазон необходимых поверхностных сопротивлений слоя составит  $10 \div 10^5$  Ом/□. Получение пленок с поверхностными сопротивлениями слоя более  $10^4$  Ом/□ представляет собой сложную задачу.

Помимо требований к удельному сопротивлению, предъявляются определенные требования и к его стабильности. Кроме того, резистивные пленки должны характеризоваться низким температурным коэффициентом сопротивления ТКС (менее  $10^{-4} 1/^\circ C$ ).

Таблица 2.2 – Свойства материалов подложек ГИС

| Параметр                                                                         | Материал               |                        |                        |                         |                                              |                              |                              |                  |

|----------------------------------------------------------------------------------|------------------------|------------------------|------------------------|-------------------------|----------------------------------------------|------------------------------|------------------------------|------------------|

|                                                                                  | Стекло                 |                        | Ситалл<br>CT50-1       | Павлен-<br>ный<br>кварц | Керамика                                     |                              |                              |                  |

|                                                                                  | C41-1                  | C48-3                  |                        |                         | 22ХС<br>(96%Al <sub>2</sub> O <sub>3</sub> ) | Поликор                      | Глазуро-<br>ванная           | BeO              |

| Класс чистоты обра-<br>ботки поверхности                                         | 14                     | 14                     | 13 - 14                | 14                      | 12                                           | 12 - 14                      | 14                           | -----            |

| Температурный коэф.<br>линейного расширения при<br>$T=20\div300^{\circ}\text{C}$ | $(41\pm2)\cdot10^{-7}$ | $(48\pm2)\cdot10^{-7}$ | $(50\pm2)\cdot10^{-7}$ | $55\cdot10^{-7}$        | $(60\pm5)\cdot10^{-7}$                       | $(70\text{-}75)\cdot10^{-7}$ | $(73\text{-}78)\cdot10^{-7}$ | $70\cdot10^{-7}$ |

| Коэффициент тепло-<br>проводности, Вт/(м·°C)                                     | 1                      | 1,5                    | 1,5                    | 7-15                    | 10                                           | 30 - 45                      | 1,2 - 1,7                    | 210              |

| Диэлектрическая про-<br>ниаемость при $f=10^6$ Гц и<br>$T=20^{\circ}\text{C}$    | 7,5                    | 3,2 - 8                | 5 – 8,5                | 3,8                     | 10,3                                         | 10,5                         | 13 – 16                      | 6,4 – 9,5        |

| Тангенс угла диэлектрических<br>потерь при $f=10^6$ Гц и $T=20^{\circ}\text{C}$  | $20\cdot10^{-4}$       | $15\cdot10^{-4}$       | $20\cdot10^{-4}$       | -                       | $6\cdot10^{-4}$                              | $10\cdot10^{-4}$             | $18\cdot10^{-4}$             | $16\cdot10^{-4}$ |

| Объемное сопротивление при<br>$T=25^{\circ}\text{C}$ , Ом·см                     | $10^{17}$              | $10^{14}$              | -                      | $10^{15}$               | -                                            | -                            | -                            | $10^{14}$        |

| Электрическая<br>прочность, кВ/мм                                                | 40                     | 40                     | -                      | -                       | 50                                           | -                            | 50                           | 20               |

Материалы, используемые для тонкопленочных резисторов, можно разделить на три группы: металлы; металлические сплавы; металлокерамические смеси – керметы.

Удельное сопротивление массивных металлов не превышает  $20\div50$  мкОм·см даже для таких материалов, как титан, молибден, хром, tantal. Однако при осаждении в виде тонких пленок удельное сопротивление металлов может значительно увеличиваться. Наиболее существенный вклад в повышение удельного сопротивления вносится дефектами структуры и примесями. Учитывая это, в процессе осаждения некоторых металлических пленок намеренно создаются условия для газопоглощения.

Наиболее широкое распространение для изготовления металлических резисторов имеют хром и tantal. Большой интерес к tantalу как материалу для тонкопленочных резисторов обусловлен его способностью легко окисляться при химическом анодировании. Частично окисляя пленку tantalа, можно тем самым уменьшать толщину резистивного слоя и одновременно обеспечивать защиту поверхности резистора. Кроме того, установлено, что tantalовые пленки при введении в них ряда примесей приобретают высокое поверхностное сопротивление слоя при низком температурном коэффициенте. Особенно хорошие результаты в качестве примеси дает азот.

Тонкие пленки полупроводниковых материалов не используются для изготовления резисторов в силу большого отрицательного температурного коэффициента сопротивления.

Помимо металлов, для изготовления резисторов широко используются металлические сплавы, обладающие более высоким удельным сопротивлением даже в объемных образцах. К таким сплавам, в первую очередь, относятся сплав никеля и хрома – никхром с удельным сопротивлением около 100 мкОм·см, а также никхром с добавками других материалов, например сплав никеля (74%), хрома (20%), железа (3%) и алюминия (3%) с удельным сопротивлением около 130 мкОм·см. Так же как и металлы, эти сплавы, полученные в виде тонких пленок, имеют более высокие удельные сопротивления, чем массивные образцы.

Керметы представляют собой металлодиэлектрические смеси. Созданию таких материалов и их широкому использованию для получения резисторов способствовали положительные результаты, полученные при окислении, азотировании и других методах введения примесей в металлические пленки при их отжигах. Намеренное изготовление смесей металлов и диэлектриков позволило получить наиболее высокие значения удельных сопротивлений. Удельное сопротивление пленок керметов в большой степени зависит от их состава. Поэтому точное воспроизведение состава кермета в пленке играет исключительно важную роль. Обычно для напыления применяют метод взрывного испарения.

Изучено большое число комбинаций металл – диэлектрик: Cr-SiO<sub>x</sub>, Al-SiOs, Pt-Ta<sub>2</sub>O<sub>5</sub> и др. Наилучшие результаты получены для комбинации Cr-SiO<sub>x</sub>.

Свойства наиболее распространенных материалов и резисторов на их основе сведены в табл. 2.3.

*Материалы для тонкопленочных конденсаторов.* Тонкопленочный конденсатор имеет трехслойную структуру металл – диэлектрик – металл, расположенную на изолирующей подложке. Параметры тонкопленочного конденсатора определяются в основном диэлектрическим материалом. Однако следует иметь в виду, что на свойства диэлектрика могут оказывать существенное влияние металлические обкладки. Например, может уменьшаться напряжение пробоя из-за миграции атомов металла в слой диэлектрика. Металлы с хорошей адгезией иногда создают в слое диэлектрика большие напряжения. Сопротивление металлических обкладок влияет на потери энергии в конденсаторе. Поэтому при разработке конденсаторов необходимо выбирать совместно всю совокупность входящих в их структуру материалов.

К основным характеристикам диэлектрических материалов для конденсаторов относятся диэлектрическая постоянная  $\epsilon$  и электрическая прочность  $E_d$ . Из-за сложности получения бездефектных пленок на большой площади максимальная площадь конденсатора ограничивается. Минимальная площадь ограничивается заданной точностью. Отсюда для обеспечения

широкого диапазона номиналов емкостей предъявляют определенные требования к удельным емкостям. Поскольку существует предел и для минимальной толщины пленок (из-за влияния проколов в пленке диэлектрика на ее электрическую прочность), то при изготовлении тонкопленочных конденсаторов к диэлектрическим материалам предъявляются определенные требования по диэлектрической проницаемости. Если ограничить толщину пленки значением 0,1 мкм, а максимально допустимую площадь соответственно 10 мм<sup>2</sup>, то для получения емкости 10<sup>6</sup> пФ требуемая диэлектрическая проницаемость составит более 10.

Электрическая прочность диэлектрического материала определяет напряжение пробоя  $U_d = E_d h$ , а следовательно, и диапазон рабочих напряжений конденсатора.

Диэлектрические материалы должны обладать минимальной гигроскопичностью, высокой механической прочностью при циклических изменениях температуры, хорошей адгезией к подложкам.

Диэлектрические материалы, используемые для тонкопленочных конденсаторов в основном представляют собой окислы полупроводников и металлов.

Из окислов полупроводников наибольшее распространение в тонкопленочной технологии получили окисел кремния SiO и окисел германия GeO, имеющие высокую диэлектрическую проницаемость. Пленки двуокиси кремния SiO<sub>2</sub> существенно реже используются в тонкопленочной технологии, что отчасти связано с более низкими значениями диэлектрической проницаемости, а также с невозможностью использования для осаждения SiO<sub>2</sub> метода вакуумного термического испарения. Наибольший интерес представляет ряд окислов тугоплавких металлов, таких как Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, HfO<sub>2</sub>, Nb<sub>2</sub>O<sub>5</sub>. Эти материалы по сравнению с другими окислами обладают наиболее высокими значениями диэлектрической проницаемости. Технология получения этих пленок развита далеко не в равной мере. Наиболее отработана технология пленок Ta<sub>2</sub>O<sub>5</sub>.

Интерес к пленкам tantalа и Ta<sub>2</sub>O<sub>5</sub> объясняется возможностью его применения для изготовления и резисторов, и конденсаторов в одних и тех же технологических процессах:

ионно-плазменного распыления и электролитического анодирования. Однако следует учитывать, что сопротивление обкладок из tantalа велико в сравнении с другими материалами

Таблица 2.3 – Основные параметры материалов тонкопленочных резисторов

| Материал                            |                                                                                    | Параметры                                                                             |                                                            |                                                                                |                                                                                             |

|-------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Для напыления<br>резистивной пленки | Контактных<br>площадок                                                             | Удельное по-<br>верхностное<br>сопротивление<br>резистивной<br>пленки $\rho_s$ , Ом/□ | Диапазон номиналь-<br>ных значений сопро-<br>тивлений, Ом  | Допустима<br>я удельная<br>мощность<br>рассеяния<br>$P_0$ , Вт/см <sup>2</sup> | Температурный<br>коэффициент<br>сопротивления<br>TKC при<br>$T= -60\div125^{\circ}\text{C}$ |

| Нихром, проволока X20H80            | Медь                                                                               | 300                                                                                   | 50 – 30 000                                                | 2                                                                              | $1 \cdot 10^{-4}$                                                                           |

| Нихром,<br>проводка                 | Золото с подслоем<br>хрома                                                         | 10                                                                                    | 1 – 10 000                                                 |                                                                                | $-2,25 \cdot 10^{-4}$                                                                       |

|                                     |                                                                                    | 50                                                                                    | 5 – 50 000                                                 |                                                                                |                                                                                             |

| Сплав МЛТ-3М                        | Медь с подслоем ванадия (луженая)<br>Медь с подслоем никрома (зашитченная никелем) | 500                                                                                   | 50 – 50 000                                                |                                                                                | $2 \cdot 10^{-4}$                                                                           |

| Хром                                | Медь (луженая)                                                                     | 500                                                                                   | 50 – 30 000                                                | 1                                                                              | $0,6 \cdot 10^{-4}$                                                                         |

| Кермет К-50С<br>(ETO.021.013 ТУ)    | Золото с подслоем<br>хрома (нихрома)                                               | 3000<br>5000<br>10 000                                                                | 1000 – 10 000<br>500 – 200 000<br>10 000 – 10 <sup>6</sup> | 2                                                                              | $3 \cdot 10^{-4}$<br>$-4 \cdot 10^{-4}$<br>$-5 \cdot 10^{-4}$                               |

Окончание табл. 2.3

| Материал                                                 |                                | Параметры                                                                                            |                                                           |                                                                                |                                                                                           |

|----------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Для напыления<br>резистивной пленки                      | Контактных<br>площадок         | Удельное по-<br>верхностное<br>сопротивление<br>резистивной<br>пленки $\rho_s$ ,<br>$\Omega/\square$ | Диапазон номиналь-<br>ных значений сопро-<br>тивлений, Ом | Допустима<br>я удельная<br>мощность<br>рассеяния<br>$P_0$ , Вт/см <sup>2</sup> | Температурны<br>й коэффициент<br>сопротивления<br>при<br>$T = -60 \div 125^\circ\text{C}$ |

| Тантал ТВЧ; лента<br>толщиной 0,3–3 мм<br>(РЭТУ 1244-67) | Алюминий с<br>подслоем ванадия | 20 – 100                                                                                             | 100 – 10 000                                              | 3                                                                              | $-2 \cdot 10^{-4}$                                                                        |

|                                                          | Медь с подслоем<br>нихрома     | 100                                                                                                  | 50 – 100 000                                              |                                                                                |                                                                                           |

|                                                          | Тантал                         | 10                                                                                                   | 10 – 15 000                                               |                                                                                |                                                                                           |

| Сплав PC-3001<br>(ETO.021.034 ТУ)                        | Золото с подслоем<br>нихрома   | 1000                                                                                                 | 100 – 50 000                                              | 2                                                                              | $-0,2 \cdot 10^{-4}$                                                                      |

|                                                          |                                | 2000                                                                                                 | 200 – 100 000                                             |                                                                                |                                                                                           |

| Сплав PC-3710<br>(ETO.021.034 ТУ)                        |                                | 3000                                                                                                 | 1000 – 200 000                                            |                                                                                | $-3 \cdot 10^{-4}$                                                                        |

Таблица 2.4 – Основные параметры диэлектрических материалов тонкопленочных конденсаторов

| Материал                               |                        | Параметры                                            |                                |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

|----------------------------------------|------------------------|------------------------------------------------------|--------------------------------|--------------------------------------------------------|----------------------------------------------------------------|------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Для напыления диэлектрика              | Для напыления обкладок | Удельное поверхностное сопротивление пленки обкладок | Удельная емкость $C_o$ , пФ/см | Диэлектрическая проницаемость $\epsilon$ при $f=1$ кГц | Тангенс угла диэлектрических потерь $\tg \delta$ при $f=1$ кГц | Электрическая прочность $E_{IPR}$ , В/см | Рабочая частота $f$ , МГц не более | Температурный коэффициент емкости ТКЕ при $T=-60 \div 125^\circ\text{C}$ , $1^\circ\text{C}$                                                                 |  |  |  |

| Моноокись кремния                      | Алюминий A99           | 0,2                                                  | 5 000                          | 5,0 – 6,0                                              | 0,01 – 0,02                                                    | $(2\text{--}3) \cdot 10^6$               | 500                                | $2 \cdot 10^{-4}$                                                                                                                                            |  |  |  |

| Моноокись германия                     |                        |                                                      | 10 000                         |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

| Боросиликатное стекло (ETO.035.015 ТУ) |                        |                                                      | 5 000                          | 11 – 12                                                | $0,005 \text{ -- } 0,007$                                      | $1,0 \cdot 10^6$                         | 300                                | $3 \cdot 10^{-4}$                                                                                                                                            |  |  |  |

|                                        |                        |                                                      | 10 000                         |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

|                                        |                        |                                                      | 15 000                         |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

|                                        |                        |                                                      | 2 500                          | 4                                                      | $0,001 \text{ -- } 0,0015$                                     | $(3\text{--}4) \cdot 10^6$               |                                    | $0,35 \cdot 10^{-4}$                                                                                                                                         |  |  |  |

|                                        |                        |                                                      | 5 000                          |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

|                                        |                        |                                                      | 10 000                         | 5,2                                                    | $0,002 \text{ -- } 0,003$                                      |                                          |                                    | $(0,5 \text{ -- } 1) \cdot 10^{-4}$<br>при $T = -60 \div 25^\circ\text{C}$ ,<br>$(1,5 \text{ -- } 1,8) \cdot 10^{-4}$<br>при $T = 25 \div 155^\circ\text{C}$ |  |  |  |

|                                        |                        |                                                      | 15 000                         |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

|                                        |                        |                                                      | 20 000                         |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

|                                        |                        |                                                      | 30 000                         |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

|                                        |                        |                                                      | 40 000                         |                                                        |                                                                |                                          |                                    |                                                                                                                                                              |  |  |  |

Окончание табл. 2.4

| Материал                                           |                                                    | Параметры                                                                        |                                       |                                                                |                                                                        |                                                       |                                           |                                                                                             |

|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|

| Для напыления диэлектрика                          | Для напыления обкладок                             | Удельное поверхностное сопротивление пленки обкладок<br>$\rho_s, \Omega/\square$ | Удельная емкость $C_o, \text{ пФ/см}$ | Диэлектрическая проницаемость $\epsilon$ при $f=1 \text{ кГц}$ | Тангенс угла диэлектрических потерь $\tg \delta$ при $f=1 \text{ кГц}$ | Электрическая прочность $E_{\text{пр}}, \text{ В/см}$ | Рабочая частота $f, \text{ МГц не более}$ | Температурный коэффициент емкости ТКЕ при $T=-60 \div 125^\circ\text{C}, 1/\text{^\circ C}$ |

| Пятиокись тантала (электрохимическое анодирование) | Тантал ТВЧ нижняя обкладка                         | 1-10                                                                             | 60 000                                | 23                                                             | 0,02                                                                   | $2 \cdot 10^6$                                        | 0,1                                       | $4 \cdot 10^{-4}$                                                                           |

|                                                    | Алюминий А99 с подслоем ванадия (верхняя обкладка) |                                                                                  | 100 000                               |                                                                |                                                                        |                                                       |                                           |                                                                                             |

| Диоксид кремния                                    | Алюминий                                           | 0,2                                                                              | 200 000                               | 4                                                              | 0,01                                                                   | $5 \cdot 10^6$                                        | 500                                       | $2 \cdot 10^{-4}$                                                                           |

(например, алюминием). Поэтому конденсаторы в тонкопленочных микросхемах, изготовленных на основе tantalа, характеризуются большими потерями энергии.

Свойства материалов, наиболее широко используемых для создания тонкопленочных конденсаторов, представлены в табл. 2.4.

*Тонкопленочные проводники.* Тонкопленочные проводники в микросхемах служат для соединения пассивных тонкопленочных элементов и создания контактных площадок для присоединения навесных элементов и внешних выводов. Тонкопленочные проводящие материалы должны иметь следующие свойства: высокую электропроводность; хорошую адгезию к подложке; способность к сварке или пайке; химическую инертность.

К материалам с высокой электрической проводимостью относятся золото, серебро, алюминий, медь. Однако пленки этих металлов не удовлетворяют всей перечисленной совокупности свойств. Например, благородные металлы имеют плохую адгезию к подложке, алюминиевые пленки плохо поддаются пайке и сварке, медь легко окисляется.

Таблица 2.5 – Материалы тонкопленочных проводников

| Материал |          | Сопротивление слоя, Ом/□ |

|----------|----------|--------------------------|

| Слой     | Покрытие |                          |

| Золото   | –        | 0,03÷0,04                |

| Медь     | Никель   | 0,02÷0,04                |

| Медь     | Серебро  | 0,02÷0,04                |

| Алюминий | Никель   | 0,05÷0,1                 |

Поэтому для получения тонкопленочных проводников используются многослойные композиции. Эти композиции включают подслой толщиной  $(1\div3)\cdot10^{-2}$  мкм из материала, обеспечивающего хорошую адгезию, слой из материала с высокой электропроводностью толщиной 0,4÷0,8 мкм и покрытие толщиной  $(5\div8)\cdot10^{-2}$  мкм из химически инертного материала с хорошей способностью к сварке или пайке. Некоторые композиции для тонкопленочных проводников, если в качестве подслоя используется никром, представлены в табл. 2.5.

При расчете пленочных проводников необходимо учитывать ряд требований, предъявляемых к характеристикам микросхемы. Среди них можно выделить следующие: сопротивление проводника не должно превышать некоторого максимального значения  $R_{\max}$ ; плотность тока, протекающего через проводник, не должна превышать значения, определяемого отношением  $I_{\max}/S_{\min}$ , где  $S_{\min}$  – площадь сечения проводника; собственные емкость и индуктивность проводника не должны быть больше некоторого максимального значения.

В гибридных микросхемах используют два типа контактных переходов. Первый представляет собой контактную пару из резистивной и низкоомной пленок, второй – контактную пару из двух низкоомных пленок.

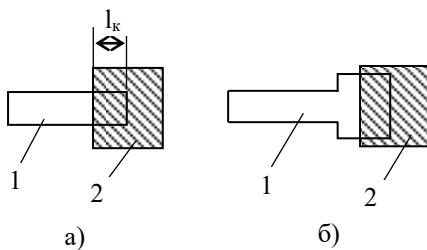

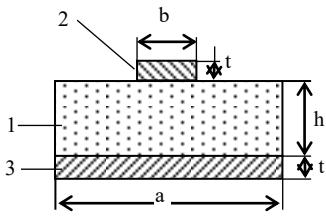

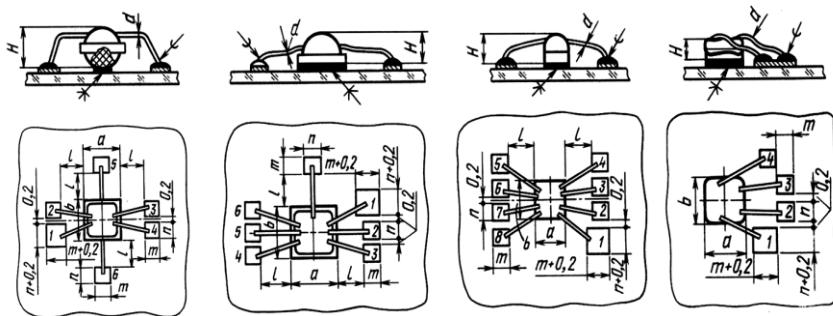

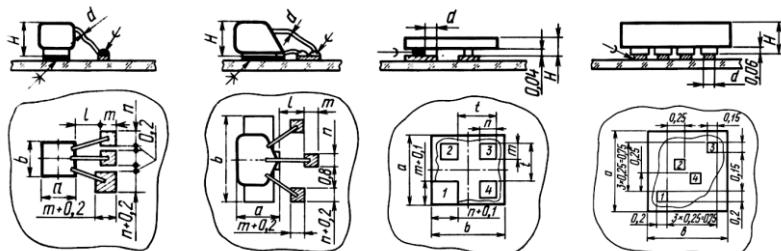

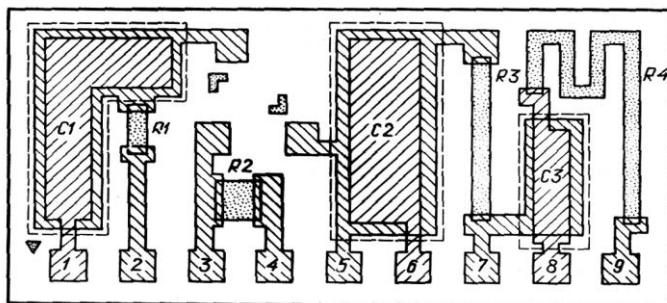

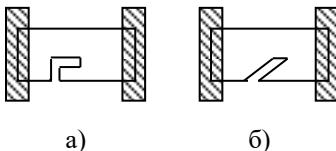

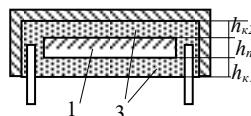

Конструкции контактных переходов между резистивными и низкоомными пленками показаны на рис. 2.1.

Рис. 2.1 – Конструкции пленочных контактов:

1 – резистивная пленка;

2 – проводящая пленка

Сопротивление подобных контактов определяется следующим образом:

$$R_k = \sqrt{\frac{\rho_s \cdot \rho_k}{b}},$$

где  $\rho_s$  – сопротивление квадрата резистивной пленки, Ом/ $\square$ ;  $\rho_k$  – удельное сопротивление контактного переходного слоя, Ом·мм<sup>2</sup>;  $b$  – ширина резистивной пленки.

Переходный слой образуется между контактирующими пленками, его удельное сопротивление зависит от технологических условий получения контакта. При напылении тонких резистивных и проводящих пленок на одной и той же вакуумной установке в одном технологическом цикле без

разгерметизации удельное сопротивление составит  $\rho_k = 0,05 \div 0,25 \text{ Ом} \cdot \text{мм}^2$ . Если между операциями напыления имел место значительный временной разрыв, в течение которого подложки находились в атмосфере воздуха, то удельное сопротивление переходного слоя возрастет до значений  $\rho_k = 2,5 \div 5,0 \text{ Ом} \cdot \text{мм}^2$ .

Рассчитанное сопротивление контакта не должно превышать допустимого, т.е.  $R_k \leq R_{k,\text{доп}}$ . Допустимое сопротивление контакта определяется по формуле

$$R_{k,\text{доп}} = R \cdot \gamma_{R_k} / 2,$$

где  $\gamma_{R_k}$  – погрешность переходных сопротивлений контактов. Длина пленочного контактного перехода  $l_k$  (рис. 2.1, *a*) для микросхем, конфигурации элементов в которых создаются с помощью масок или трафаретов, должна отвечать соотношению

$$l_k \geq 1,5 \sqrt{\frac{\rho_k}{\rho_s}}.$$

В большинстве случаев  $l_k$  принимают равным 0,1–0,2 мм. Если конфигурации пленочных элементов создаются с помощью фотолитографии, то первоначально на подложку напыляется сплошная резистивная пленка, затем сплошная проводящая, после чего ненужные участки пленок удаляются фотолитографией. Таким образом, под всеми проводящими дорожками существуют резистивные пленки.

### 2.3 Расчет конструкций тонкопленочных резисторов

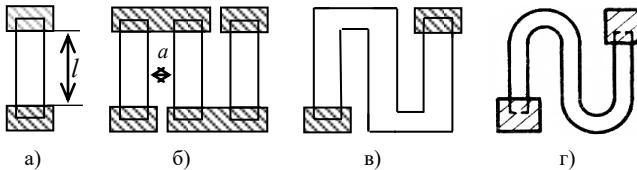

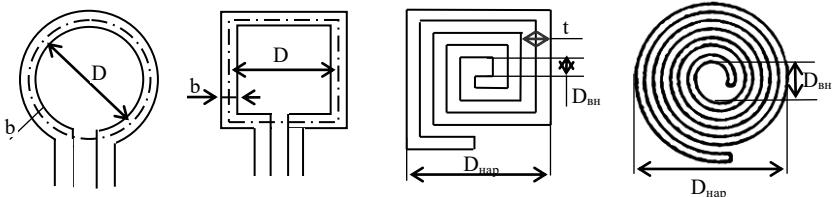

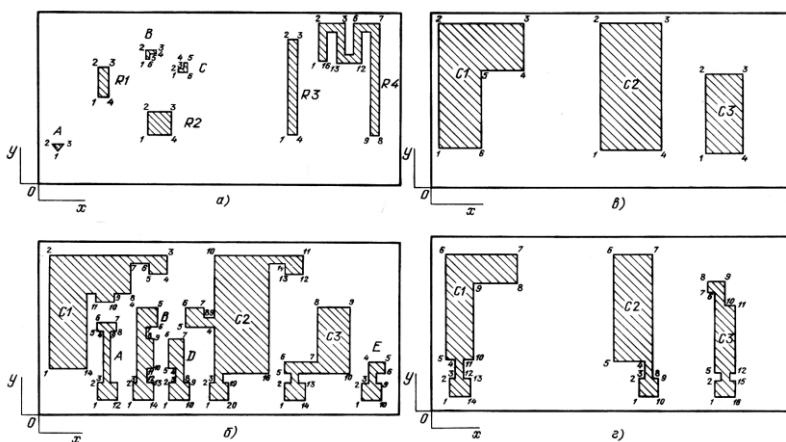

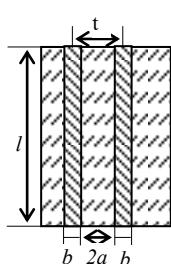

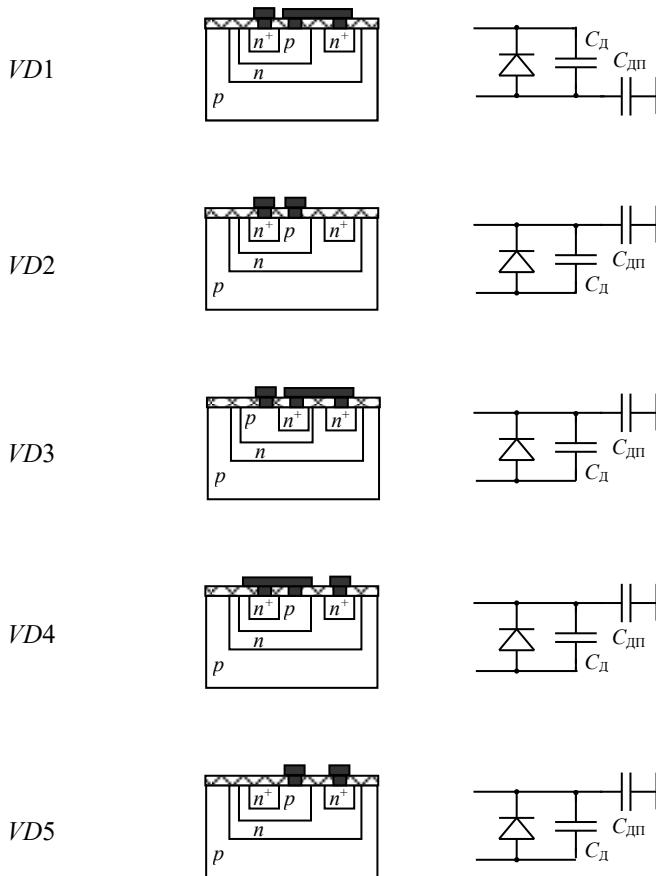

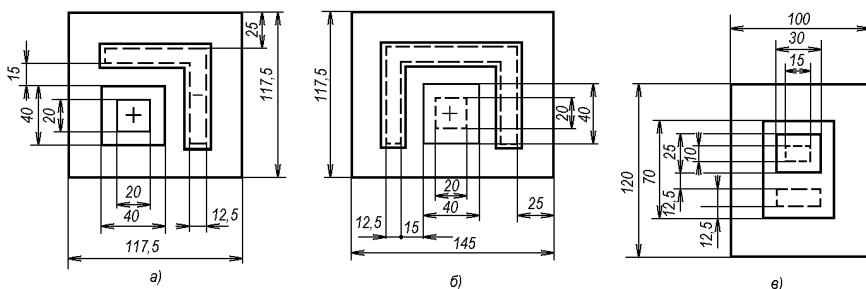

*Конфигурации тонкопленочных резисторов.* Типовые конфигурации тонкопленочных резисторов приведены на рис. 2.2, *a-г*. Наиболее распространенной является прямоугольная форма как самая простая по технологическому исполнению. Резистор в виде полосок занимает большую площадь, чем резисторы типа «меандр» или «змейка».

Рис. 2.2 – Конфигурация тонкопленочных резисторов:

а – полоска; б – составной из полосок; в – меандр; г – змейка.

Меандр уступает в отношении стабильности и надежности конструкции типа «змейка» из-за перегрева в уголках, но он предпочтительнее с точки зрения изготовления фотошаблонов и поэтому более распространен.

Контактные площадки следует располагать с противоположных сторон резистора для устранения погрешности совмещения проводящего и резистивного слоев. По этой причине придавать резисторам форму, изображенную на рис. 2.3, не рекомендуется, так как сопротивление таких резисторов зависит от точности совмещения масок и фотошаблонов (неточности при совмещении изменяют длину таких резисторов).

*Конструктивный расчет тонкопленочных резисторов.* Конструктивный расчет тонкопленочных резисторов заключается в определении формы, геометрических размеров и минимальной площади, занимаемой резисторами на подложке. При этом необходимо, чтобы резисторы обеспечивали рассеивание заданной мощности при удовлетворении требуемой точности  $\gamma_R$  в условиях существующих технологических возможностей.

Исходные данные для расчета: номинал резистора  $R_i$ , Ом; допуск на номинал  $\gamma_{R^i}$ , %; мощность рассеяния  $P_i$ , мВт; рабочий диапазон температур  $T_{max} - T_{min}$ , °C; технологические ограничения; шаг координатной сетки, мм.

Рис. 2.3 – Конфигурация резисторов, сопротивление которых зависит от погрешности совмещения

Порядок расчета:

1. Определяют оптимальное с точки зрения минимума площади под резисторами ГИС сопротивление квадрата резистивной пленки:

$$\rho_{S_{onm}} = \sqrt{\frac{\sum_i^n R_i}{\sum_i^1 1/R_i}}, \quad (2.1)$$

где  $n$  – число резисторов;

$R_i$  – номинал  $i$ -го резистора.

2. По табл. 2.3 выбирают материал резистивной пленки с удельным сопротивлением, ближайшим по значению к вычисленному  $\rho_{Sonm}$ . При этом необходимо, чтобы ТКС материала был минимальным, а удельная мощность рассеяния  $P_0$  – максимальной.

3. Производят проверку правильности выбранного материала с точки зрения точности изготовления резисторов.

Полная относительная погрешность изготовления пленочного резистора  $\gamma_R = \Delta R/R$  состоит из суммы погрешностей:

$$\gamma_R = \gamma_{Kf} + \gamma_{\rho s} + \gamma_t + \gamma_{Rct} + \gamma_{Rk},$$

где  $\gamma_{Kf}$  – погрешность коэффициента формы;  $\gamma_{\rho s}$  – погрешность воспроизведения величины  $\rho s$  резистивной пленки;  $\gamma_t$  – температурная погрешность;  $\gamma_{Rct}$  – погрешность, обусловленная старением пленки;  $\gamma_{Rk}$  – погрешность переходных сопротивлений контактов.

Погрешность воспроизведения удельного поверхностного сопротивления  $\gamma_{\rho s}$  зависит от условий напыления и материала резистивной пленки. В условиях серийного производства ее значение не превышает 5%.

Температурная погрешность зависит от ТКС материала пленки:

$$\gamma_t = \alpha_R (T_{max} - 20^\circ C),$$

где  $\alpha_R$  – температурный коэффициент сопротивления материала пленки,  $1/\text{ }^\circ\text{C}$ .

Погрешность  $\gamma_{Rct}$ , обусловленная старением пленки, вызвана медленным изменением структуры пленки во времени и ее окислением. Она зависит от материала пленки и эффективности защиты, а также от условий хранения и эксплуатации. Обычно для ГИС  $\gamma_{Rct}$  не превышает 3%.

Погрешность переходных сопротивлений контактов  $\gamma_{Rk}$  зависит от технологических условий напыления пленок, удельного сопротивления резистивной пленки и геометрических размеров контактного перехода: длины перекрытия контактирующих пленок, ширины резистора. Обычно  $\gamma_{Rk} = 1\div 2\%$ . Если материал контактных площадок выбран в соответствии с табл. 2.3, то этой погрешностью можно пренебречь.

**Допустимая погрешность коэффициента формы**

$$\gamma_{Kf} = \gamma_R - \gamma_{ps} - \gamma_i - \gamma_{Rcm} - \gamma_{Rk}.$$

Если значение  $\gamma_{Kf}$  отрицательно, то это означает, что изготовление резистора заданной точности из выбранного материала невозможно. В этом случае необходимо выбрать другой материал с меньшим ТКС либо использовать подгонку резисторов, если позволяет технологическое оборудование.

4. Определяют конструкцию резисторов по значению коэффициента формы  $K_f$ :

$$K_{fi} = R_i / \rho_s.$$

При  $1 \leq K_{fi} \leq 10$  рекомендуется конструировать резистор прямоугольной формы, изображенный на рис. 2.2, а, при  $K_{fi} > 10$  – резистор сложной формы (составной, меандр или типа «змейка», рис. 2.2, б-г), при  $0,1 \leq K_{fi} \leq 1$  – резистор прямоугольной формы, у которого длина меньше ширины. Конструировать резистор с  $K_{fi} < 0,1$  не рекомендуется, так как он будет иметь большие контактные площадки и занимать значительную площадь на подложке.

Если в одной схеме содержатся низкоомные и высокоомные резисторы, можно использовать два резистивных материала, для выбора которых определяют  $\rho_s$  сначала для всех резисторов по формуле (2.1), после чего разбивают резисторы на две группы так, чтобы  $R_{i max}$  первой группы было меньше, а  $R_{i min}$  второй группы – больше значения  $\rho_{Sopt}$ , вычисленного для всех

резисторов. Затем по этой же формуле рассчитывают  $\rho_{\text{сопт1}}$  и  $\rho_{\text{сопт2}}$  и выбирают материалы для каждой группы резисторов в отдельности.

5. Дальнейший расчет проводят в зависимости от формы резисторов.

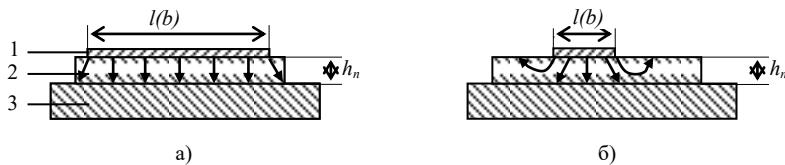

*Расчет прямоугольных полосковых резисторов.* Для резисторов, имеющих  $K_\phi > 1$  (рис. 2.4, а, б), сначала определяют ширину, а затем длину резистора. Расчетное значение ширины резистора должно быть не менее наибольшего значения одной из трех величин:

$$b_{\text{расч}} \geq \max \{b_{\text{техн}}, b_{\text{точн}}, b_p\},$$

где  $b_{\text{техн}}$  – минимальная ширина резистора, определяемая возможностями технологического процесса;  $b_{\text{точн}}$  – ширина резистора, определяемая точностью изготовления:

$$b_{\text{точн}} \geq \frac{\Delta b + \Delta l / K_\phi}{\gamma K_\phi}, \quad (2.2)$$

где  $\Delta l$ ,  $\Delta b$  – погрешности изготовления ширины и длины резистора, зависящие от метода изготовления;  $b_p$  – минимальная ширина резистора, при которой обеспечивается заданная мощ-

$$b_p = \sqrt{\frac{P \rho_s}{P_0 R}} = \sqrt{\frac{P}{P_0 K_\phi}}. \quad (2.3)$$

ность: За ширину  $b$  резистора принимают ближайшее к  $b_{\text{расч}}$  большее значение, кратное шагу координатной сетки, принятому для чертежа топологии с учетом

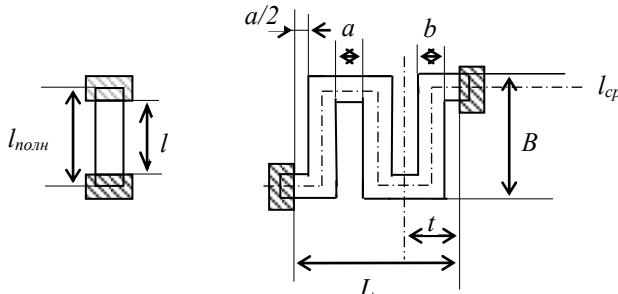

Рис. 2.4 – К расчету резисторов типа «полоска» (а) и «мейндр» (б)

масштаба. Для тонкопленочной технологии шаг координатной сетки обычно составляет 1 или 0,5 мм. Например, если шаг координатной сетки 1 мм, масштаб 20:1, то округление производят до величины, кратной 0,05 мм.

Далее находят расчетную длину резистора:

$$l_{\text{расч}} = b K_{\phi}.$$

За длину  $l$  резистора принимают ближайшее к  $l_{\text{расч}}$  значение, кратное шагу координатной сетки, принятому для чертежа топологии с учетом масштаба. При этом следует оценивать получающуюся погрешность и при необходимости выбирать большее значение ширины  $b$  резистора, при котором округление длины  $l_{\text{расч}}$  дает приемлемую погрешность.

Определяют полную длину резистора с учетом перекрытия контактных площадок:

$$l_{\text{полн}} = l + 2e,$$

где  $e$  – размер перекрытия резистора и контактных площадок.

При использовании метода двойной фотолитографии  $l_{\text{полн}} = l$ .

Площадь, занимаемая резистором на подложке,  $S = l_{\text{полн}} \cdot b$ .

Для резисторов, имеющих  $K_{\phi} < 1$ , сначала определяют длину, а затем ширину резистора.

Расчетное значение длины резистора  $l_{\text{расч}}$  выбирают из условия

$$l_{\text{расч}} \geq \max \{l_{\text{техн}}, l_{\text{точн}}, l_p\},$$

где  $l_{\text{техн}}$  – минимальная длина резистора, определяемая разрешающей способностью выбранного метода формирования конфигурации (см. Приложение 1);  $l_{\text{точн}}$  – минимальная длина резистора, при которой обеспечивается заданная точность:

$$l_{\text{точн}} \geq \frac{\Delta l + \Delta b \cdot K_{\phi}}{\gamma K_{\phi}}, \quad (2.4)$$

$l_p$  – минимальная длина резистора, при которой рассеивается заданная мощность:

$$l_p = \sqrt{\frac{P \cdot K_{\phi}}{P_0}}. \quad (2.5)$$

За длину  $l$  резистора принимают ближайшее к  $l_{\text{расч}}$  значение, кратное шагу координатной сетки, принятому для чертежа топологии.

Расчетную ширину резистора определяют по формуле

$$b_{\text{расч}} = \frac{l}{K_{\phi}}. \quad (2.6)$$

За ширину  $b$  резистора принимают ближайшее к  $b_{\text{расч}}$  значение, кратное шагу координатной сетки. При этом следует оценивать получающуюся погрешность и при необходимости корректировать значение длины  $l$  резистора в большую сторону, при котором округление ширины  $b_{\text{расч}}$  дает приемлемую погрешность.

Затем определяют полную длину резистора с учетом перекрытия контактных площадок и площадь резистора.

Для проверки находят действительную удельную мощность и погрешность резистора. Очевидно, резистор спроектирован удовлетворительно, если:

1) удельная мощность рассеяния  $P_0$  не превышает допустимого значения  $P_0$ :

$$P_0' = P / S \leq P_0;$$

2) погрешность коэффициента формы  $\gamma_{K\phi}$  не превышает допустимого значения  $\gamma_{K\phi \text{ доп}}$ :

$$\gamma'_{K\phi} = \Delta l / l_{\text{полн}} + \Delta b / b \leq \gamma_{K\phi \text{ доп}}.$$

*Конструктивный расчет тонкопленочных резисторов сложной формы.*

При конструировании резистора в виде отдельных резистивных полосок, соединенных проводящими перемычками (см. рис. 2.2, б), сумма длин резистивных полосок должна быть равна длине, определенной по формуле:

$$l = b \cdot K_{\phi}.$$

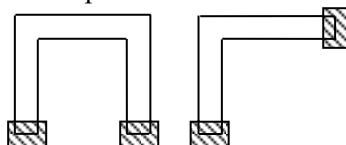

Резисторы типа «меандр» (рис. 2.2, в) рассчитывают из условия минимальной площади, занимаемой резистором.

Расчет меандра проводят после определения ширины  $b$  резистора в такой последовательности.

Определяют длину средней линии меандра:

$$l_{\text{ср}} = b \cdot K_{\phi}.$$

Задают расстояние между резистивными полосками  $a$ . С учетом технологических ограничений (см. Приложение 1) при масочном методе  $a_{min}=300$  мкм, при фотолитографии  $a_{min}=100$  мкм (обычно задают  $a = b$ ).

Находят шаг одного звена меандра:

$$t = a + b. \quad (2.7)$$

Определяют оптимальное число звеньев меандра  $n_{opt}$  из условия, чтобы площадь, занимаемая резистором типа «меандр», была минимальной. Очевидно, это будет в случае, когда меандр вписывается в квадрат ( $L = B$ ).

Если отношение длины средней линии меандра к ширине резистивной полоски больше 10, то оптимальное число звеньев меандра может быть вычислено по приближенной формуле

$$n_{opt} \approx \sqrt{\frac{l_{cp}L}{tB}}. \quad (2.8)$$

При  $L = B$  (меандр квадратной формы) и  $a = b$  выражение упрощается:

$$n_{opt} \approx \sqrt{\frac{K_\Phi}{2}}. \quad (2.9)$$

Значение  $n_{opt}$  округляют до ближайшего целого.

Определяют длину меандра:

$$L = n \cdot (a + b). \quad (2.10)$$

Вычисляют ширину меандра:

$$B = \frac{l_{cp} - an}{n}, \quad (2.11)$$

где  $n$  – оптимальное число звеньев меандра, округленное до ближайшего целого.

Расстояние  $a$  выбирают из конструктивно-технологических соображений. Например, при напылении резисторов через маску размер  $a_{min}$  определяется минимально возможным расстоянием между соседними щелями в маске. Для обеспечения требуемой жесткости маски оно должно удовлетворять условию

$$B_{max}/a \leq 10.$$

Если это условие не выполняется, необходимо изменить расстояние  $a$  и вновь вычислить  $n_{opt}$ ,  $L$ ,  $B$ . Для

фотолитографического метода указанное условие некритично.

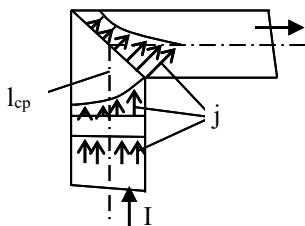

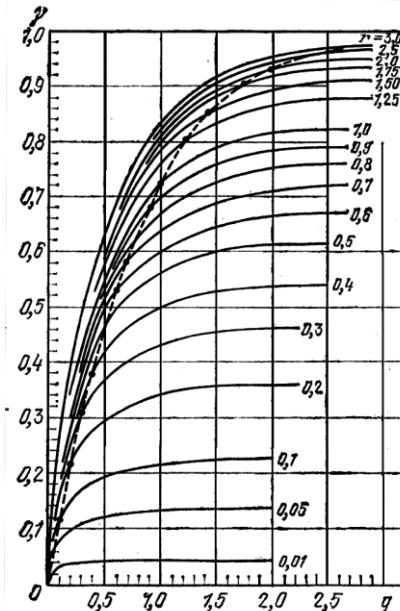

Приведенные расчетные соотношения не учитывают, что в резисторах типа «меандр» плотность тока в изгибах неравномерна (рис. 2.5). Это приводит к сокращению электрической длины пленочного резистора и уменьшению его сопротивления. Неравномерное распределение плотности тока наблюдается в пределах трех квадратов области изгиба (рис. 2.6, *a*, *b*).

Рис. 2.5 – Распределение плотности тока в резисторах типа «меандр»

Рис. 2.6 – Конструкции изгибов пленочных резисторов типа «меандр»: а – изгиб под прямым углом; б – П-образный изгиб

Для уточненного расчета с учетом изгибов конструкцию резистора типа «меандр» можно представить в виде последовательно соединенных прямолинейных участков и изгибов. При этом его сопротивление можно определить как сумму сопротивлений прямолинейных участков и изгибов:

$$R = R_u m + \frac{l_n n}{b} \rho_s, \quad (2.12)$$

где  $R_u$  – сопротивление изгибов;  $m$  – число изгибов,  $l_n$  – длина прямолинейных участков;  $n$  – число звеньев меандра.

Для изгиба под прямым углом (рис. 2.6, *a*)  $R_u = 2,55 \rho_s$  для П-образного изгиба (рис. 2.6, *b*)  $R_u = (a/b+3) \rho_s$ . Отсюда длина прямолинейного участка одного звена меандра

$$l_n = \frac{R - mR_u}{\rho_s n} b. \quad (2.13)$$

После этого корректируют размеры  $L$  и  $B$  с целью обеспечения заданного номинала резистора.

Квадратная или близкая к ней форма резистора типа «меандр» часто оказывается неудобной при компоновке пленочных элементов на подложке микросхемы, например, из-за отличной от квадрата площади, отводимой под резистор. Тогда, зная габаритную площадь меандра и задавшись одним из размеров меандра (например,  $B$ ), определяют второй размер  $L$  и число звеньев меандра  $n$ .

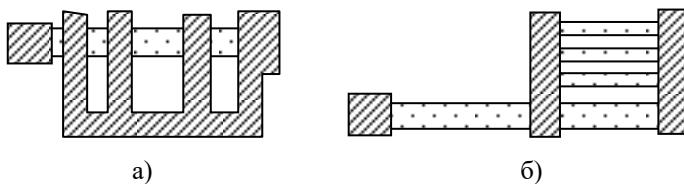

В некоторых схемах требуется использовать резисторы, точность получения которых превышает точность, обеспечиваемую возможностями принятого технологического способа изготовления. В этих случаях при конструировании гибридной микросхемы применяют специальные пленочные резисторы (рис. 2.7), сопротивление которых перед монтажом микросхем подвергается подгонке и не выходит за пределы малых допусков.

Рис. 2.7 – Конструкции пленочных резисторов со ступенчатой подгонкой сопротивления: а – путем добавления секций перерезанием перемычек; б – уменьшением числа параллельно подключенных резистивных дорожек

Наиболее распространены способы подгонки сопротивления пленочных резисторов перерезанием пленки резцом манипулятора или испарением части материала резистора с помощью луча лазера.

## 2.4 Тонкопленочные конденсаторы

Наряду с резисторами, пленочные конденсаторы относятся к числу наиболее распространенных элементов гибридных схем.

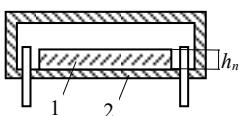

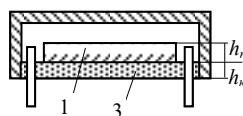

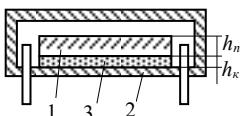

По конструкции пленочные конденсаторы чаще всего представляют собой трехслойную структуру металл – диэлектрик – металл и состоят из нижней и верхней обкладок, разделенных слоем диэлектрического материала.

К конструкции конденсаторов предъявляется ряд конструктивно-технологических требований: минимальные габаритные размеры; воспроизводимость характеристик в процессе производства; совместимость технологии их изготовления с процессами производства других элементов гибридной интегральной схемы.

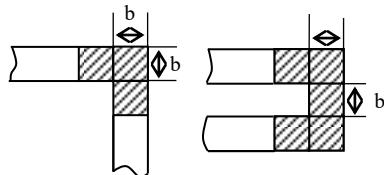

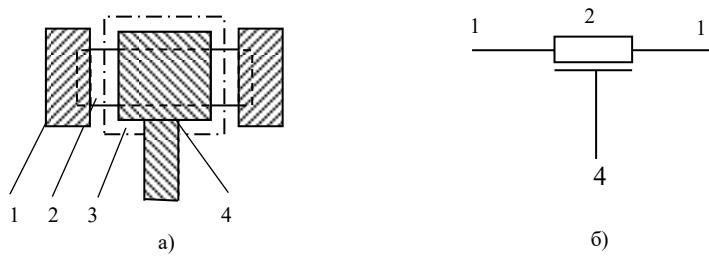

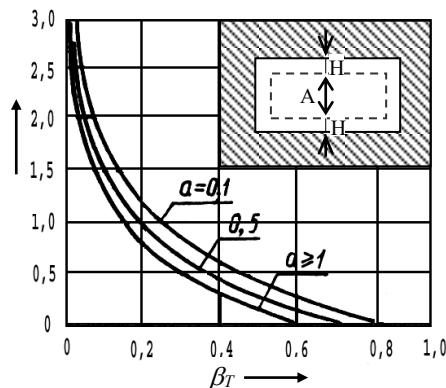

Конструкция, изображенная на рис. 2.8, *a*, характерна для конденсаторов с повышенной емкостью (сотни – тысячи пикофарад). Ее особенностью является то, что контур верхней обкладки полностью вписывается в контур нижней обкладки. Эта конструкция имеет следующие положительные качества: неточность совмещения контуров обкладок не оказывается на величине емкости; контур диэлектрика заходит за пределы обеих обкладок. В этом случае гарантируется надежная изоляция обкладок по периферии конденсатора при предельном их несовмещении.

Пленочный конденсатор с большой емкостью может иметь сложную конфигурацию, отличную от прямоугольной, причем линии периметра обкладок обязательно пересекаются под прямым углом. При разработке топологии микросхемы конструктор может полностью использовать свободные участки площади подложки.

Конструкция пленочного конденсатора, изображенная на рис. 2.8, *б*, характерна для конденсаторов с небольшой емкостью (десятки пикофарад), когда для получения необходимой емкости достаточна площадь взаимного перекрытия двух коммутационных проводников, разделенных пленкой диэлектрика. Емкость рассматриваемого конденсатора нечувствительна к смещению обкладок из-за неточности совмещения.

Рис. 2.8 – Конструкции пленочных конденсаторов:

1 – верхняя обкладка; 2 – нижняя обкладка; 3 – диэлектрик

При активной площади пленочного конденсатора менее  $5 \text{ mm}^2$  начинает сказываться краевой эффект, причем тем сильнее, чем меньше площадь. Если расчетная площадь конденсатора менее  $1 \text{ mm}^2$ , его можно выполнять в виде двух последовательно соединенных конденсаторов (рис. 2.8, в).

В высокочастотных конструкциях применяют гребенчатые конденсаторы (рис. 2.8, г). Роль обкладок выполняют пленочные проводники в форме гребенки. Здесь используется составной диэлектрик: подложка – воздух или подложка – диэлектрическое покрытие. Гребенчатые конденсаторы и конденсаторы в виде двух параллельно расположенных полосок используются тогда, когда необходимо получить емкость единицы и доли пикофарад.

При малых емкостях (единицы или доли пикофарад), когда расчетная площадь пленочного МДМ-конденсатора слишком мала и технология не позволяет его выполнить в виде трехслойной пленочной структуры, можно формировать конденсатор в виде двух параллельных проводящих полосок.

Исходными данными для конструктивного расчета тонкопленочных конденсаторов являются следующие: номинальная емкость  $C$ ,  $\Phi$ ; допуск на номинал  $\gamma_C$ , %; рабочее напряжение  $U_p$ , В; рабочая частота  $f$ , Гц; рабочий диапазон температур  $T_{max} - T_{min}$ , °С.

Емкость пленочного конденсатора определяется по формуле:

$$C = \frac{\varepsilon \cdot \varepsilon_0 \cdot S_e \cdot k_{kp}}{d}, \quad (2.14)$$

где  $S_e$  – площадь верхней обкладки,  $d$  – толщина пленки,  $k_{kp}$  – коэффициент, учитывающий влияние краевого эффекта.

На первом этапе выбирают материал диэлектрика по рабочему напряжению в соответствии с данными, приведенными в табл. 2.4. Чтобы конденсатор занимал как можно меньшую площадь, выбирается материал с возможно более высокими диэлектрической проницаемостью, электрической прочностью, а также малыми значениями ТКЕ и  $tg\delta$ .

Далее определяют минимальную толщину диэлектрика из условия электрической прочности

$$d \geq \frac{U_p \cdot k_3}{E_{np}}, \quad (2.15)$$

где  $E_{np}$  – электрическая прочность выбранного диэлектрика,  $U_p$  – рабочее напряжение,  $K_3$  – коэффициент запаса (2...4) в зависимости от условий эксплуатации.

Толщина диэлектрической пленки должна быть в пределах 0,1...1 мкм, в противном случае следует выбирать другой материал диэлектрика. При толщине диэлектрика менее 0,1 мкм увеличивается вероятность короткого замыкания обкладок. При толщине диэлектрика более 1 мкм возможен разрыв верхней обкладки в месте вывода из-за большой ступеньки по толщине пленки. Оптимальная толщина диэлектрика 0,3...0,5 мкм.

Затем вычисляют максимально допустимую относительную погрешность воспроизведения активной площади конденсатора:

$$\gamma_{S_{\text{доп}}} = \gamma_C - \gamma_{C_0} - \gamma_{C_t} - \gamma_{C_{cr}},$$

где  $\gamma_{C_0}$  – погрешность воспроизведения удельной емкости (5...10)%,

$\gamma_{C_t}$  – температурная погрешность емкости,

$\gamma_{C_t} = \alpha_C \cdot (T - 20^\circ\text{C})$ , где

$\alpha_C$  – температурный коэффициент емкости (ТКЕ),

$\gamma_{C_{ct}}$  – погрешность, обусловленная старением конденсатора (2...3%).

Оценивается удельная емкость конденсатора исходя из условия электрической прочности:

$$C'_0 = \frac{\epsilon \cdot \epsilon_0}{d} \quad (2.16)$$

и из условия заданной точности:

$$C''_0 = C \cdot \left( \frac{\gamma_{S_{\text{доп}}}}{\Delta S} \right)^2 \cdot \frac{k_\phi}{(1 + k_\phi)^2}, \quad (2.17)$$

где  $\Delta S$  – абсолютная погрешность воспроизведения размеров конденсатора,  $\Delta S=0,001\text{ см}$ ;  $k_\phi$  – коэффициент формы,  $k_\phi=A/B$ .

Окончательное значение удельной емкости  $C_0$  выбирается из условия  $C_0 = \min(C'_0 \text{ и } C''_0)$ .

Значение  $k_{kp}$  представляется как:

$$k_{kp} = \begin{cases} 1 & \text{при } C/C_0 \geq 0,05 \text{ см}^2, \\ 1,3 - 6 \cdot C/C_0 & \text{при } 0,01 \leq C/C_0 \leq 0,05 \text{ см}^2. \end{cases}$$

Определяют площадь верхней обкладки:

$$S = \frac{C}{C_0 k_{kp}}. \quad (2.18)$$

Тогда размеры верхней обкладки:

$$A_1 = \sqrt{S \cdot k_\phi}; \quad B_1 = A_1/k_\phi.$$

Размер нижней обкладки

$$A_2 = A_1 + 2(\Delta S + \eta), \quad B_2 = B_1 + 2(\Delta S + \eta) \text{ и диэлектрика}$$

$$A_3 = A_2 + 2(\Delta S + \eta), \quad B_3 = B_2 + 2(\Delta S + \eta),$$

где  $\eta$  – погрешность установки и совмещения масок.

Иногда величину  $(\Delta S + \eta)$  заменяют фиксированным значением 0,1...0,2 мм.

Добротность пленочных конденсаторов представляет собой величину, обратную тангенсу угла потерь:

$$Q = \frac{1}{\operatorname{tg}\delta_{\Sigma}}.$$

Потери в конденсаторе складываются из потерь в диэлектрике и в обкладках:

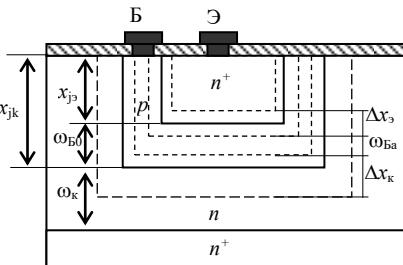

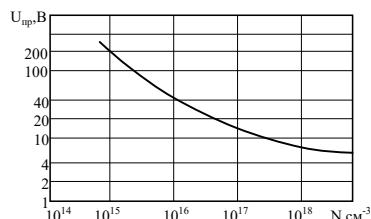

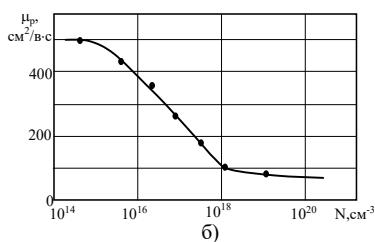

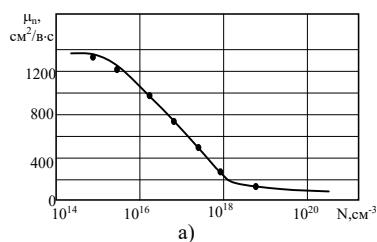

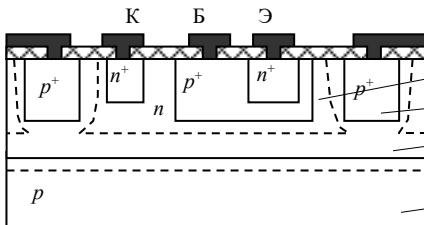

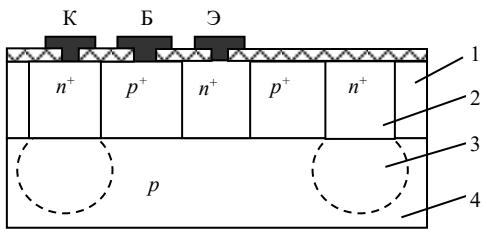

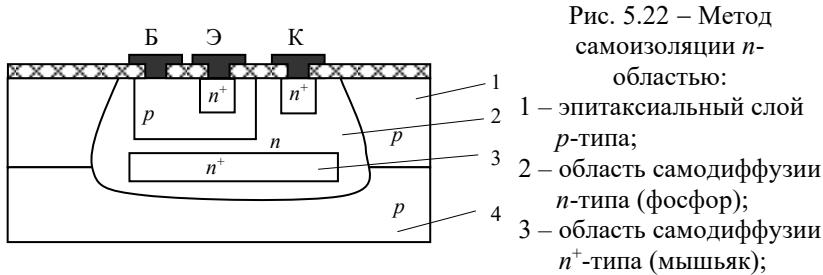

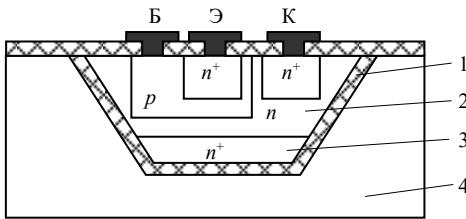

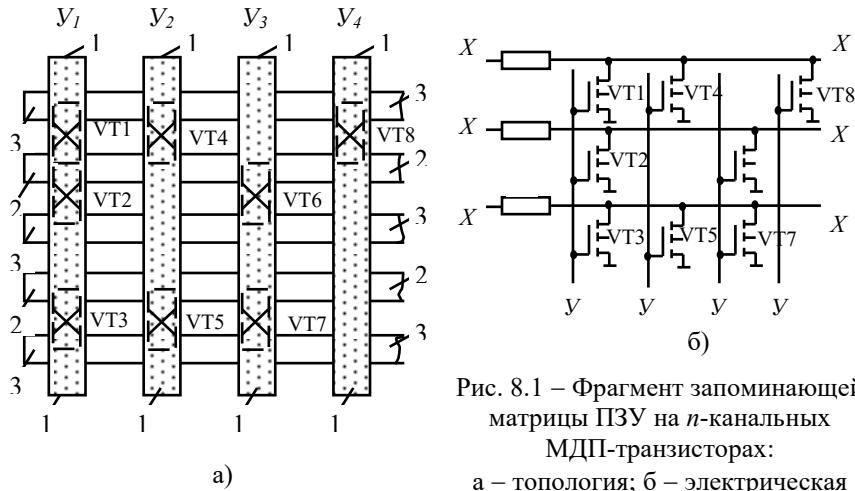

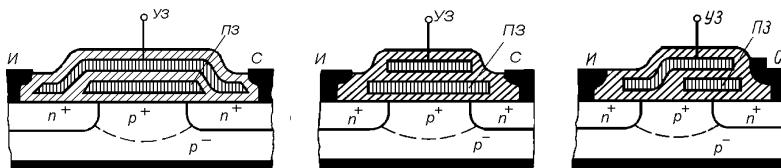

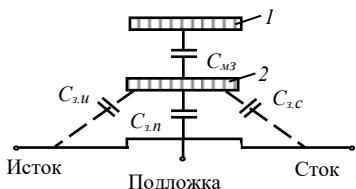

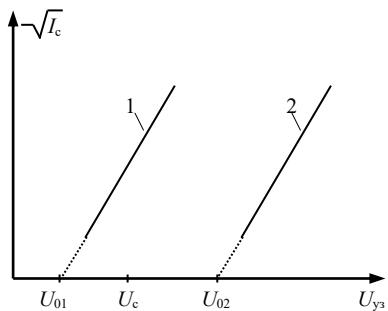

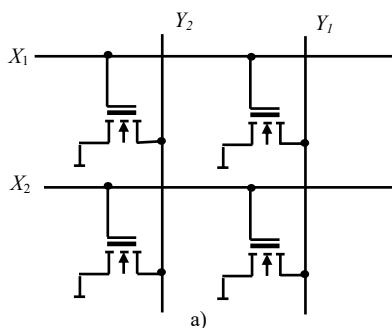

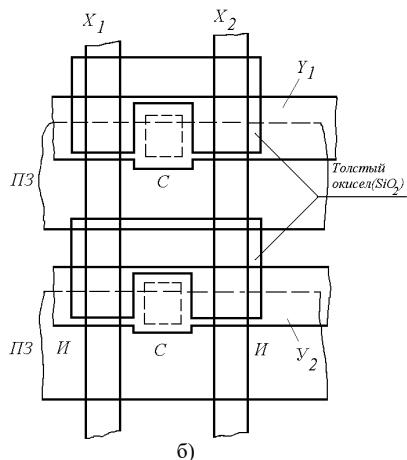

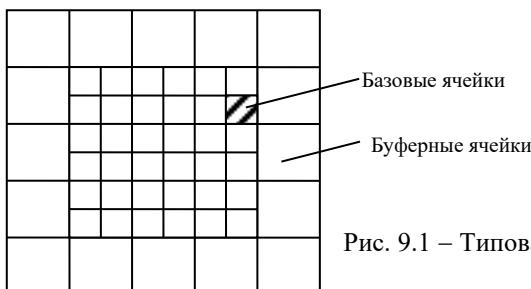

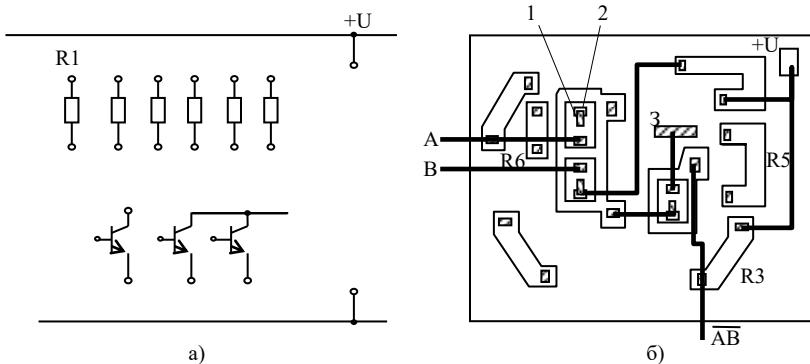

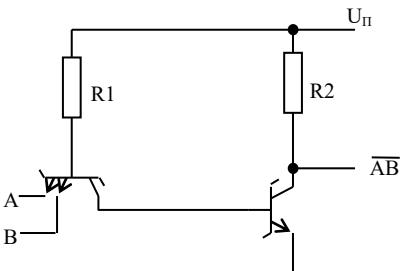

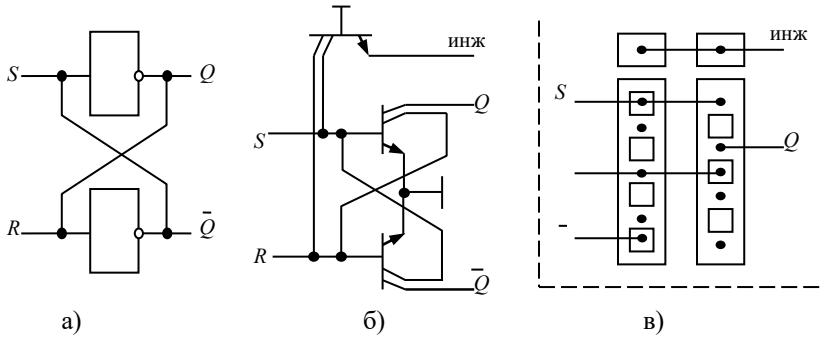

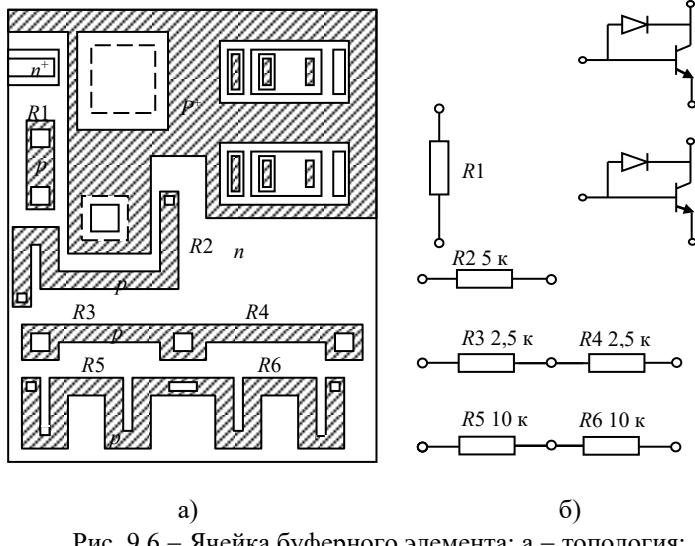

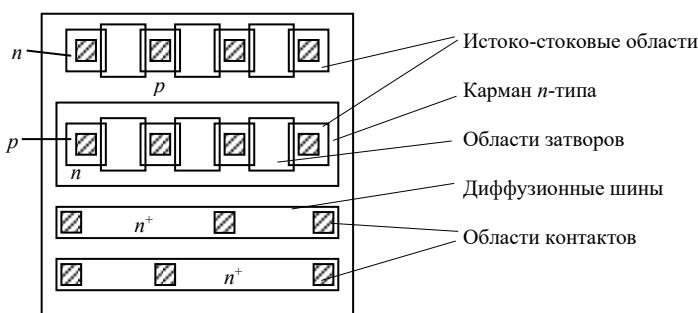

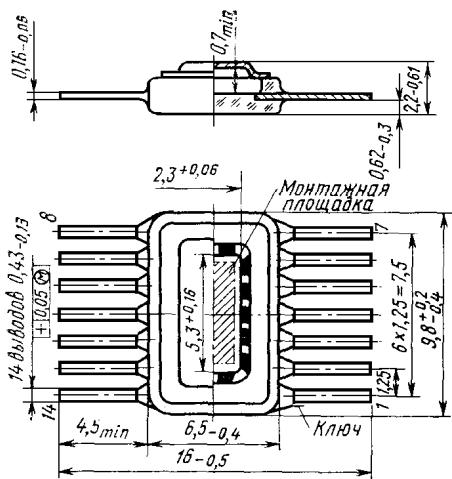

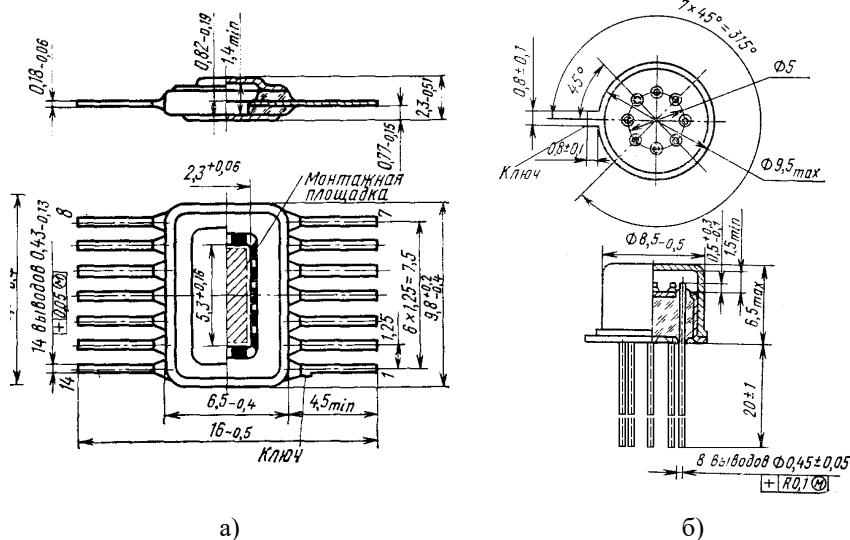

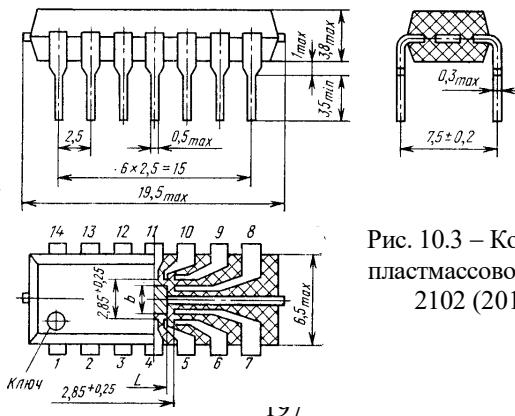

$$\operatorname{tg}\delta_{\Sigma} = \operatorname{tg}\delta_d + \operatorname{tg}\delta_{\text{обкл}}.$$