Министерство науки и высшего образования

Российской Федерации

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

**А.А. Жигальский**

**ПРОЕКИРОВАНИЕ ЭЛЕКТРОННОЙ КОМПОНЕНТНОЙ

БАЗЫ МИКРОЭЛЕКТРОНИКИ И

МИКРОСИСТЕМНОЙ ТЕХНИКИ**

Учебно-методическое пособие

по курсовому проектированию

**Томск

2025**

УДК 621.382.049.77.002(075.8)

ББК 32.844я73

Ж68

**Рецензент:**

**Троян Павел Ефимович,**

доктор технических наук, профессор кафедры физическая

электроника ФГАОУ ВО «Томский государственный

университет систем управления и радиоэлектроники»

**Жигальский, Александр Анатольевич**

Ж68 Проектирование электронной компонентной базы

микроэлектроники и микросистемной техники: Учебно-

методическое пособие по курсовому проектированию /

А.А. Жигальский. - Томск: Томск. гос. ун-т систем упр. и

радиоэлектроники, 2025. – 25 с.

Учебно-методическое пособие содержит методические указания и рекомендации по выполнению курсового проекта по дисциплине «Проектирование электронной компонентной базы микроэлектроники и микросистемной техники». В пособии рассмотрены содержание и порядок выполнения курсового проекта. Даются методические указания по проектированию и расчету полупроводниковых и гибридных интегральных схем, а также указания к составлению пояснительной записки и оформлению графической документации по курсовому проекту.

Предназначено для студентов высших учебных заведений технических специальностей.

**УДК 621.382.049.77.002(075.8)**

**ББК 32.844я73**

Одобрено на заседании кафедры физической

электроники протокол №162 от 07.11.2024 года

© Жигальский А.А., 2025

© Томск. гос. ун-т систем упр. и

радиоэлектроники, 2025

## **СОДЕРЖАНИЕ**

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| <b>ВВЕДЕНИЕ.....</b>                                                       | <b>4</b>  |

| 1 Цели и задачи курсового проекта.....                                     | 5         |

| 2 Тематика курсового проектирования.....                                   | 5         |

| 3 Содержание и оформление курсового проекта.....                           | 6         |

| 4 График выполнения курсового проекта .....                                | 7         |

| 5 Методические указания по выполнению<br>курсового проекта.....            | 8         |

| 5.1 Анализ технического задания.....                                       | 8         |

| 5.2 Обоснование конструкторского-<br>технологического варианта.....        | 9         |

| 5.3 Расчет активных элементов ИС.....                                      | 10        |

| 5.4 Расчет пассивных элементов ИС.....                                     | 10        |

| 5.5 Разработка топологии и конструкции ИС.....                             | 11        |

| <b>ЛИТЕРАТУРА .....</b>                                                    | <b>12</b> |

| Приложение 1 Правила проектирования изолированных<br>областей.....         | 13        |

| Приложение 2 Правила размещения элементов на<br>площади, кристалла.....    | 15        |

| Приложение 3 КТО при проектировании<br>тонкопленочных ГИС .....            | 17        |

| Приложение 4 КТО при проектировании ИМС на<br>биполярных транзисторах..... | 19        |

| Приложение 5 Пример оформления графического<br>материала к ПЗ.....         | 22        |

| Приложение 6 Пример оформления титульного<br>листа.....                    | 25        |

## **ВВЕДЕНИЕ**

Выполнение курсового проекта является заключительным этапом в изучении курса "Проектирование электронной компонентной базы микроэлектроники и микросистемной техники". На этом этапе студент углубляет свои знания в области теории и практики проектирования микросхем и приобретает навыки самостоятельной работы на основе использования нормативно-технической литературы.

В пособии рассмотрены содержание и порядок выполнения курсового проекта. Даются методические указания по проектированию и расчету полупроводниковых и гибридных интегральных схем (ИС), а также указания к составлению пояснительной записки (ПЗ) и оформлению графической документации по курсовому проекту.

## **1 ЦЕЛИ И ЗАДАЧИ КУРСОВОГО ПРОЕКТА**

Курсовой проект представляет собой самостоятельную работу студента, которая преследует следующие цели:

- 1) закрепить и более глубоко усвоить знания, полученные при изучении теоретической части курса;

- 2) привить навыки самостоятельной работы по решению инженерных задач комплексной проработки вопросов топологического проектирования и производства ИС;

- 3) научить студентов методам расчета топологии ИС;

- 4) привить навыки правильного оформления конструкторской документации в соответствии с требованиями ЕСКД и дополнительными требованиями отраслевых стандартов.

При курсовом проектировании выполняются в основном следующие задачи:

- 1) анализ технического задания и обоснование выбора конструктивно-технологического варианта реализации ИС;

- 2) выбор материалов, компонентов, разработка конструкции и конструкторские расчеты с применением ЭВМ по самостоятельно составленным программам и по типовым;

- 3) разработка топологии кристалла или платы: размещение элементов и компонентов, трассировка электрических соединений;

- 4) оценка уровня помех, обусловленных паразитными параметрами элементов конструкции;

- 5) расчет теплового режима элементов и компонентов;

- 6) разработка и изготовление сборочного чертежа ИС, чертежей кристалла или платы.

## **2 ТЕМАТИКА КУРСОВОГО ПРОЕКТИРОВАНИЯ**

Так как бюджет времени, отводимый студенту на курсовое проектирование, довольно ограничен, основными объектами проектирования оказываются узлы ИС, выполняющие несложные функциональные преобразования информации и ее хранение. К таким узлам относятся логические ячейки,

регистры, генераторы, усилители напряжения, тока или мощности, шифраторы, дешифраторы, компараторы и т.д.

Исходными данными для проектирования являются:

- 1) назначение проектируемой ИС;

- 2) схема электрическая принципиальная;

- 3) вариант исполнения (полупроводниковая или гибридная);

- 4) конструктивно-технологические ограничения (типовые или специальные);

- 5) условия и сроки эксплуатации и хранения (параметры климатических, механических и специальных воздействий);

- 6) требования к составу проекта.

Если для проектирования выбран узел, который может быть построен на основе нескольких (2-3) типовых логических элементов по известному алгоритму, возможно формулирование в техническом задании только требований к электрическим параметрам проектируемой ИС без представления электрической схемы.

### **3 СОДЕРЖАНИЕ И ОФОРМЛЕНИЕ КУРСОВОГО ПРОЕКТА**

Курсовой проект состоит из комплекта чертежей и пояснительной записи.

Рекомендуется следующее содержание (перечень основных разделов) пояснительной записи:

- 1) введение;

- 2) анализ технического задания и выбор конструктивно-технологического варианта ИС;

- 3) расчет элементов ИС;

- 4) разработка топологии ИС;

- 5) разработка конструкции ИС;

- 6) оценка характеристики спроектированной ИС;

- 7) заключение;

- 8) список использованных источников.

Конструкторская документация (комплект чертежей) составляется в соответствии с требованиями ЕСКД и дополнительными требованиями соответствующих отраслевых

стандартов. Перечень наиболее часто применяемых при разработке конструкторской документации на ИС стандартов ЕСКД приведен в [2].

В [3] рассмотрены правила и даны примеры оформления конструкторской документации на гибридные и полупроводниковые ИС.

Для выполнения графических документов конструкторской части проекта рекомендуются следующие форматы:

- 1) схема электрическая принципиальная - А4, А3;

- 2) сборочный чертеж - А3;

- 3) кристалл (плата) - А2, А3.

Требованием к чертежу кристалла (или платы) является увеличение размеров (для гибридных ИС - в 10-20 раз, для полупроводниковых ИС - в 200 - 500 раз). Графические документы проекта подшиваются в сложенной по установленной стандартом форме в пояснительную записку в качестве приложения.

#### **4 ГРАФИК ВЫПОЛНЕНИЯ КУРСОВОГО ПРОЕКТА**

Техническое задание на курсовой проект выдается в начале восьмого семестра. График выполнения курсового проекта тесно увязывается с расписанием занятий, отведенных по учебному плану курсового проектирования. С целью рационального использования бюджета времени при выполнении расчетно-графической части возможна разработка только определенных частных вопросов курсового проекта.

Контроль выполнения графика осуществляется на занятиях по курсовому проектированию и во время консультаций. С этой целью, проводятся контрольные собеседования в сроки, устанавливаемые преподавателем.

Курсовой проект должен быть выполнен и защищен до начала экзаменационной сессии. За неделю до защиты проект сдается на проверку руководителю. При проверке руководитель пишет краткий отзыв (замечания) на проект. Если проект возвращается на доработку, то после доработки он должен быть возвращен с предыдущим отзывом руководителя.

К защите представляется расчетно-пояснительная записка объемом 25-30 страниц и комплект чертежей: схема электрическая принципиальная, спецификация, топологический чертеж кристалла или платы, чертеж фотошаблонов, сборочный чертеж.

Захата проекта производится перед комиссией в составе руководителя проекта и членов комиссии, назначенных заведующим кафедрой. Время и место защиты утверждается предварительно.

На доклад по защите проекта отводится 5-7 минут. В докладе следует обосновать состав, содержание и результаты выполненных работ.

В ходе защиты проекта его автору могут быть заданы вопросы, как по содержанию проекта, так и по общим разделам теоретического курса.

По итогам защиты комиссия принимает решение по оценке проекта. Оценка объявляется студенту и проставляется в его зачетной книжке.

## **5 МЕТОДИЧЕСКИЕ УКАЗАНИЯ ПО ВЫПОЛНЕНИЮ КУРСОВОГО ПРОЕКТА**

### **5.1 Анализ технического задания**

В техническом задании на проектирование формулируется комплекс технических требований, которым должна удовлетворять разработанная конструкция ИС.

При анализе технического задания необходимо:

1) четко определить конструктивный состав ИС. Выяснить полноту исходных данных и технических требований, предъявляемых к разрабатываемой ИС;

2) изучить функциональные преобразования информации, осуществляемые ИС.

3) выделить требования, предъявляемые к составным частям конструкции ИС, и наметить пути их удовлетворения. По возможности указать приемлемость типовых решений по конструктивному строению ИС.

- 4) выделить требования к элементам электрической схемы и наметить пути их удовлетворения;

- 5) отметить специфические особенности электрической схемы, условий эксплуатации и производства, на которые необходимо обратить внимание при выборе конструктивно – технологического исполнения ИС;

- 6) на основании изучения материалов по пунктам 4 и 5 сформулировать, если необходимо, дополнительные требования к конструкции и технологии.

## **5.2 Обоснование конструкторско-технологического варианта**

На данном этапе в соответствии с результатами предшествующего анализа и с учетом требований по быстродействию, условий эксплуатации ИС и масштаба производства выбирается конструктивно-технологический вариант реализации ИС.

Если проектируется полупроводниковая ИС, то тип активных элементов уже задан, это биполярные, либо МОП-транзисторы. Остается выбрать способ изоляции элементов (при необходимости). В большинстве типов ИС на основе биполярных транзисторов элементы изолируются друг от друга с помощью обратно-смещенных *p-n* переходов или слоев диэлектриков [3, с. 115-121]. Способ изоляции элементов в значительной степени определяет характеристики микросхемы. Элементы на основе МОП-транзисторов с каналами одного типа проводимости, как правило, не требуют создания изолирующих структур, тогда как комплементарные полевые транзисторы необходимо изолировать друг от друга .

Далее выбирается типовая структура кристалла и укрупненный технологический процесс его изготовления (последовательность формирования элементов).

Если проектируется гибридная ИС, то обычно указываются тип активных элементов и требования к пассивным элементам по точности и стабильности, которые накладывают определенные ограничения на выбор конструктивно-

технологического варианта ее исполнения. С учётом этих ограничений, а также уровня рассеиваемой мощности и значений токов, требований к стоимости и заданного масштаба производства выбирается разновидность конструкции гибридной ИС: тонко- или толстопленочная. После того, как выбрана разновидность гибридной ИС, поступают согласно рекомендациям.

### 5.3 Расчет активных элементов ИС

Активные элементы ИС осуществляют преобразование электрической энергии. К ним относятся транзисторы (биполярные, полевые) и диоды различного назначения.

В полупроводниковых ИС топологические конфигурации биполярных транзисторов следует выбирать, руководствуясь рекомендациями в [3, с.81-93; 4; 5]. Если какой-либо из найденных параметров не удовлетворяет заданному в техническом задании значению, то следует обоснованно скорректировать технологию (т.е. структуру) и повторить процесс синтеза топологии и расчета параметров транзистора.

Топологические конфигурации полевых транзисторов (*n*-канальные МОП-транзисторы с индуцированными и встроенными каналами, а также КМОП-транзисторы) выбирают согласно с рекомендациями, содержащимися в [3, с.143-151; 4; 5].

Топологические конфигурации диодов реализуются на основе биполярных транзисторных структур с учетом ограничений и рекомендаций [3, с.93-99; 4; 5]. Для вариантов, использующих эмиттерный *p-n* переход, размеры эмиттера определяются аналогично биполярному транзистору, полагая  $I_{\text{эм}}=I_{D\text{max}}$ . Там, где используется коллекторный переход, размеры базовой области выбирают, исходя из условия  $I_{D\text{max}}[S_{\text{базы}} < 1000 \text{ A/cm}^2]$ .

В современных гибридных ИС в качестве активных компонентов применяются кристаллы полупроводниковых ИС, как правило, в бескорпусном исполнении. Сведения о

бескорпусных активных приборах для гибридных ИС приводятся в справочной литературе [3, с.48-57; 5; 6], где наряду с электрическими параметрами приведены сведения о габаритных и присоединительных размерах и способах закрепления и подключения этих приборов.

#### **5.4 Расчет пассивных элементов ИС**

К пассивным элементам ИС относятся резисторы, конденсаторы, соединения и контакты.

Полупроводниковые резисторы проектируются с учетом рекомендаций [3, с.99-108; 4; 5]. Проектирование пленочных резисторов осуществляется по методикам, приведенным в [3, с.25-34; 4; 5]. Конструкции и методика расчета подгоняемых резисторов приведены в [4,5].

Вопросы проектирования полупроводниковых конденсаторов рассмотрены в [3, с. 108-112; 4; 5]. Пленочные конденсаторы для гибридных ИС рассмотрены в [3, с.34-40; 4; 5].

#### **5.5 Разработка топологии и конструкции ИС**

Топология ИС представляет собой картину взаимного расположения и формы элементов и соединений на кристалле (плате). Общие принципы разработки топологии полупроводниковой ИС рассмотрены в [4; 5]. Исходными данными для разработки топологии ИС являются электрическая схема, технические требования и конструктивно-технологические ограничения. Перечень последних приведен в приложении. Особенности проектирования топологии фрагментов ИС на биполярных транзисторах освещены в [3, с.121-130; 4; 5]. При разработке фрагментов (элементов) широко используется принцип функциональной интеграции [3, с.155-161; 5]. Особенности проектирования фрагментов ИС на МОП-транзисторах описаны в [3, с.151-155; 4]. Разработка конструкции полупроводниковых ИС изложена в [3, 4, 5]. Выбор корпуса и способа крепления кристалла освещен в [3,

с.184-193, 4,5]. Методика и примеры расчета теплового режима ИС описаны в [3,с.130-134; 4,5]. Для полимерных, пластмассовых корпусов и в случае бескорпусной защиты оценивают герметичность по времени влагозащиты согласно [4].

Для гибридных ИС и микросборок рекомендации по конструированию и расчету тонкопленочных элементов, выбору подложек и компонентов изложены в [3, 4, 5]. Методика расчета теплового режима элементов и компонентов ГИС рассмотрена [3,с.71-77; 5].

Разработка топологии толстопленочных схем с учетом конструкторских требований и технологических ограничений кратко рассмотрена в [3, с.64-69].

## ЛИТЕРАТУРА

1. Пономарев М.Ф. , Коноплев Б.Г. Конструирование и расчет микросхем и микропроцессоров. – М.: Радио и связь, 1986.–176 с.

2. Матсон Э.А., Крыжановский Д.В. Справочное пособие по конструированию микросхем. – Минск, Высшая школа, 1982. – 224 с.

3. Жигальский А.А. Проектирование и конструирование микросхем: Учебное пособие. – Томск: ТУСУР, 2007. – 195 с.

4. Конструирование и технология микросхем / Под ред. Л.А. Коледова. М.: Высшая школа, 1984. – 231 с.

5. Пономарев М.Ф. Конструирование и расчет интегральных схем. – М.: Радио и связь, 1982.

## ПРИЛОЖЕНИЕ 1

### Правила проектирования изолированных областей

- 1) суммарная площадь изолирующих  $p-n$ -переходов должна быть минимальной, так как их емкость является паразитной. Минимальные размеры изолированной области определяются геометрическими размерами находящихся в ней элементов и зазорами, которые необходимо выдерживать между краем изолированной области и элементами и между самими элементами, размещенными в одной изолированной области;

- 2) к изолирующим  $p-n$ -переходам всегда должно быть приложено напряжение обратного смещения, что практически осуществляется подсоединением подложки  $p$ -типа, или области разделительной диффузии  $p$ -типа, к точке схемы с наиболее отрицательным потенциалом. При этом суммарное обратное напряжение, приложенное к изолирующему  $p-n$ -переходу, не должно превышать напряжения пробоя;

- 3) диффузионные резисторы, формируемые на основе базового слоя, можно располагать в одной изолированной области, которая подключается к точке схемы с наибольшим положительным потенциалом. Обычно такой точкой является контактная площадка ИМС, на которую подается напряжение смещения от коллекторного источника питания;

- 4) резисторы на основе эмиттерного и коллекторного слоев следует располагать в отдельных изолированных областях;

- 5) транзисторы типа  $n-p-n$ , коллекторы которых подсоединенны непосредственно к источнику питания, целесообразно размещать в одной изолированной области вместе с резисторами;

- 6) транзисторы типа  $n-p-n$ , которые включены по схеме с общим коллектором, можно располагать в одной изолированной области;

- 7) все другие транзисторы, кроме упомянутых в п. 5 и 6, необходимо располагать в отдельных изолированных областях, т.е. все коллекторные области, имеющие различные потенциалы, должны быть изолированы;

8) для уменьшения паразитной емкости между контактными площадками и подложкой, а также для защиты от короткого замыкания в случае нарушения целостности пленки окисла под ними при приварке проволочных выводов под каждой контактной площадкой создают изолированную область, за исключением контактных площадок с наиболее отрицательным потенциалом;

9) количество изолированных областей для диодов может сильно изменяться в зависимости от типа диодов и способов их включения. Если в качестве диодов используются переходы база-коллектор, то для каждого диода требуется отдельная изолированная область, так как каждый катод (коллекторная область *n*-типа) должен иметь отдельный вывод. Если в качестве диодов используются переходы эмиттер – база, то все диоды можно поместить в одной изолированной области. При этом все катоды диодов (эмиттерные области) сформированы отдельно в общем аноде;

10) для диффузионных конденсаторов требуются отдельные изолированные области. Исключение составляют случаи, когда один из выводов конденсатора является общим с другой изолированной областью;

11) для диффузионных перемычек всегда требуются отдельные изолированные области.

## ПРИЛОЖЕНИЕ 2

### **Правила размещения элементов ИМС на площади кристалла.**

- 1) при размещении элементов ИМС и выполнении зазоров между ними необходимо строго выполнять ограничения, соответствующие типовому технологическому процессу;

- 2) резисторы, у которых нужно точно выдерживать отношение номиналов, должны иметь одинаковую ширину и конфигурацию и располагаться рядом друг с другом. Это относится и к другим элементам ИМС, у которых требуется обеспечить точное соотношение их характеристик;

- 3) резисторы с большой мощностью не следует располагать вблизи активных элементов;

- 4) диффузионные резисторы можно пересекать проводящей дорожкой поверх слоя окисла кремния, покрывающего резистор;

- 5) форма и место расположения конденсаторов не являются критичными;

- 6) соединения, используемые для ввода питания, заземления, входной и выходной выводы необходимо выполнять в виде широких и коротких полосок, что уменьшает паразитные сопротивления;

- 7) для улучшения развязки между изолированными областями контакт к подложке следует располагать рядом с мощным транзистором или как можно ближе ко входу или выходу схемы;

- 8) число внешних выводов в схеме, а также порядок расположения и обозначения контактных площадок выводов ИМС на кристалле должны соответствовать выводам корпуса;

- 9) коммутация в ИМС должна иметь минимальное количество пересечений и минимальную длину проводящих дорожек. Если полностью избежать пересечений не удается, коммутацию можно осуществить, формируя дополнительные контакты к коллекторным областям транзисторов, применяя диффузионные перемычки;

10) первую контактную площадку располагают в нижнем левом углу кристалла и отличают от остальных по ее положению относительно фигур совмещения или заранее оговоренных элементов топологии.

Нумерацию остальных контактных площадок проводят против часовой стрелки. Контактные площадки располагают в зависимости от типа выбранного корпуса по периметру кристалла или по двум противоположным его сторонам;

11) фигуры совмещения располагают одной-двумя группами на любом свободном месте кристалла;

12) при разработке аналоговых ИМС элементы входных дифференциальных каскадов должны иметь одинаковую топологию и быть одинаково ориентированными в плоскости кристалла; для уменьшения тепловой связи входные и выходные каскады должны быть максимально удалены; для уменьшения высокочастотной связи через подложку контакт к ней следует осуществлять в двух точках – вблизи входных и выходных каскадов.

### ПРИЛОЖЕНИЕ 3

#### Конструктивно-технологические ограничения при проектировании тонкопленочных ГИС

| Содержание ограничения                                                                                                                                                                                        | Размер ограничения, мм,<br>при использовании<br>метода |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------|

|                                                                                                                                                                                                               | Ф                                                      | МФ   |

| Точность изготовления линейных размеров пленочных элементов и расстояний между ними $\Delta l$ , $\Delta b$ , $\Delta a$ , $\Delta L$ , $\Delta B$ и других при расположении пленочных элементов в одном слое | 0,01                                                   | 0,01 |

| Минимально допустимый размер резистора, $l, b$                                                                                                                                                                | 0,1                                                    | 0,3  |

| Минимально допустимые расстояния между пленочными элементами, расположенными в одном слое, $a$                                                                                                                | 0,1                                                    | 0,3  |

| Максимально допустимое соотношение размеров $l/a$                                                                                                                                                             | 100                                                    | 30   |

| Минимальное расстояние от пленочных элементов до края платы, $d$                                                                                                                                              | 0,2                                                    | 0,5  |

| Минимальная ширина пленочных проводников, $i$                                                                                                                                                                 | 0,05                                                   | 0,1  |

| Минимально допустимое расстояние между краем пленочного резистора и краем его контактной площадки, $j$                                                                                                        | 0,1                                                    | 0,2  |

| Минимально допустимое расстояние между краями диэлектрика и нижней обкладки конденсатора, $f$                                                                                                                 |                                                        | 0,1  |

| Минимально допустимое расстояние между краями верхней и нижней обкладок конденсатора, $g$                                                                                                                     |                                                        | 0,2  |

| Минимально допустимое расстояние между краем диэлектрика и соединением вывода конденсатора с другим пленочным элементом, $h$                                                                                  |                                                        | 0,3  |

| Минимально допустимое расстояние от пленочного конденсатора до приклеиваемых навесных компонентов, $z$                                                                                                        |                                                        | 0,5  |

| Минимальная площадь перекрытия обкладок конденсатора $L \times B$                                                                                                                                             | $0,5 \times 0,5$                                       |      |

| Содержание ограничения                                                                                                                                              | Размер ограничения, мм,<br>при использовании<br>метода |         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------|

|                                                                                                                                                                     | Ф                                                      | МФ      |

| Минимально допустимое расстояние от проволочного проводника или вывода до края контактной площадки или до края пленочного проводника, не защищенного изоляцией, $k$ |                                                        | 0,2     |

| Минимальные размеры контактных площадок для монтажа навесных компонентов с шариковыми или столбиковыми выводами                                                     |                                                        | 0,2×0,2 |

| Минимальные размеры контактных площадок для контроля электрических параметров                                                                                       |                                                        | 0,2×0,2 |

| Минимальное расстояние между контактными площадками для приварки и припайки проволочных проводников                                                                 |                                                        | 0,2     |

| Максимальная длина гибкого вывода без дополнительного крепления                                                                                                     |                                                        | 3,0     |

| Минимальное расстояние между контактными площадками для монтажа навесных компонентов с шариковыми или столбиковыми выводами и пленочным резистором                  |                                                        | 0,6     |

| Минимальное расстояние между контактными площадками для монтажа навесных компонентов с шариковыми или столбиковыми выводами и дизелектриком конденсатора            |                                                        | 0,35    |

| Минимальное расстояние от края навесного компонента до края платы                                                                                                   |                                                        | 0,4     |

| Минимальное расстояние от края навесного компонента до края другого компонента                                                                                      |                                                        | 0,4     |

| Минимальное расстояние от края навесного компонента до края контактной площадки, предназначенный для приварки проволочных выводов                                   |                                                        | 0,4     |

| Минимальное расстояние от края навесного компонента до проволочного проводника                                                                                      |                                                        | 0,3     |

Ф – фотолитографический;

МФ – комбинированный (масочный и фотолитографический).

## ПРИЛОЖЕНИЕ 4

### Конструктивно-технологические ограничения при проектировании ИМС на биполярных транзисторах

| Содержание ограничения                                                                              | Размер ограничения, мкм |

|-----------------------------------------------------------------------------------------------------|-------------------------|

| Ширина линии скрабирования слоя                                                                     | 60                      |

| Расстояние от центра скрабирующей полосы до края слоя металлизации или до края диффузионной области | 50-100                  |

| Размер контактных площадок для термокомпрессионной приварки проводников                             | 100×100                 |

| Расстояние между контактными площадками                                                             | 70                      |

| Размер контактных площадок тестовых элементов                                                       | 50×50                   |

| Ширина проводника при длине < 50 мкм                                                                | 4                       |

| Ширина проводника при длине ≥ 50 мкм                                                                | 6                       |

| Расстояние между проводниками                                                                       | 3                       |

| Ширина области разделительной диффузии                                                              | 4                       |

| Расстояние от базы до области разделительной диффузии                                               | 10                      |

| Расстояние между краем области подлегирования коллекторного контакта и краем разделительной области | 10                      |

| Расстояние между краем разделительной области и краем скрытого $n^+$ -слоя                          | 10                      |

| Расстояние между краем контактного окна в окисли к коллектору и краем базы                          | 7                       |

| Расстояние между краем контактного окна в окисли к базе и краем базы                                | 3                       |

| Расстояние между эмиттерной и базовой областями                                                     | 3                       |

| Расстояние между краем контактного окна в окисли к эмиттеру и краем эмиттера                        | 3                       |

| Расстояние между контактным окном к базе и эмиттером                                                | 4                       |

| Расстояние между базовыми областями, сформированными в одном коллекторе                             | 9                       |

| Расстояние между эмиттерными областями, сформированными в одной базе                                | 6                       |

| Содержание ограничения                                                                                                | Размер ограничения, мкм |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------|

| Расстояние между контактным окном к коллектору и областью разделительной диффузии                                     | 10                      |

| Размеры контактного окна к базе                                                                                       | 4×6                     |

| Размеры контактного окна к эмиттеру                                                                                   | 4×4                     |

| Ширина области подлегирования $n^+$ -слоя в коллекторе                                                                | 8                       |

| Ширина контактного окна к коллектору                                                                                  | 4                       |

| Ширина резистора                                                                                                      | 5                       |

| Размеры окна в окисли                                                                                                 | 2,5×2,5                 |

| Перекрытие металлизации контактных окон в окисли к элементам                                                          | 2                       |

| Расстояние от края контактного окна к $p^+$ -разделительным областям для подачи смещения до края области разделения   | 6                       |

| Расстояние от края контактного окна к изолированным областям $n$ -типа для подачи смещения до края области разделения | 6                       |

| Ширина диффузионной перемычки                                                                                         | 3                       |

| Размер окна в пассивирующем окисле                                                                                    | 100×100                 |

| Расстояние от края окна в пассивации до края контактной площадки                                                      | 6                       |

| Расстояние между соседними резисторами                                                                                | 7                       |

| Расстояние между диффузионными и ионно-легированными резисторами                                                      | 4                       |

| Расстояние между контактной площадкой и проводящей дорожкой                                                           | 20                      |

| Ширина скрытого $n^+$ -слоя                                                                                           | 4                       |

| Расстояние между контактными площадками тестовых элементов                                                            | 40                      |

## ПРИЛОЖЕНИЕ 5

Пример оформления графического материала к ПЗ

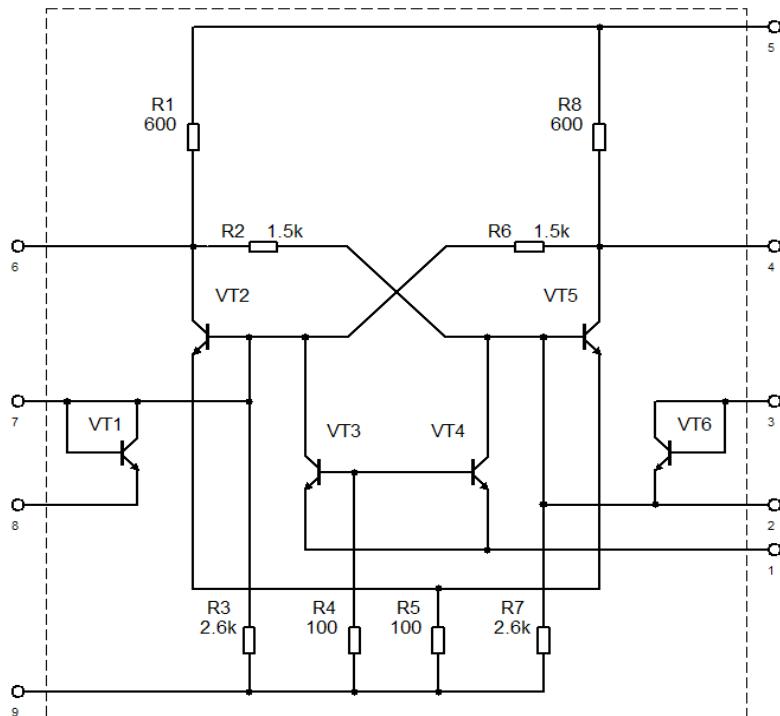

Схема электрическая принципиальная

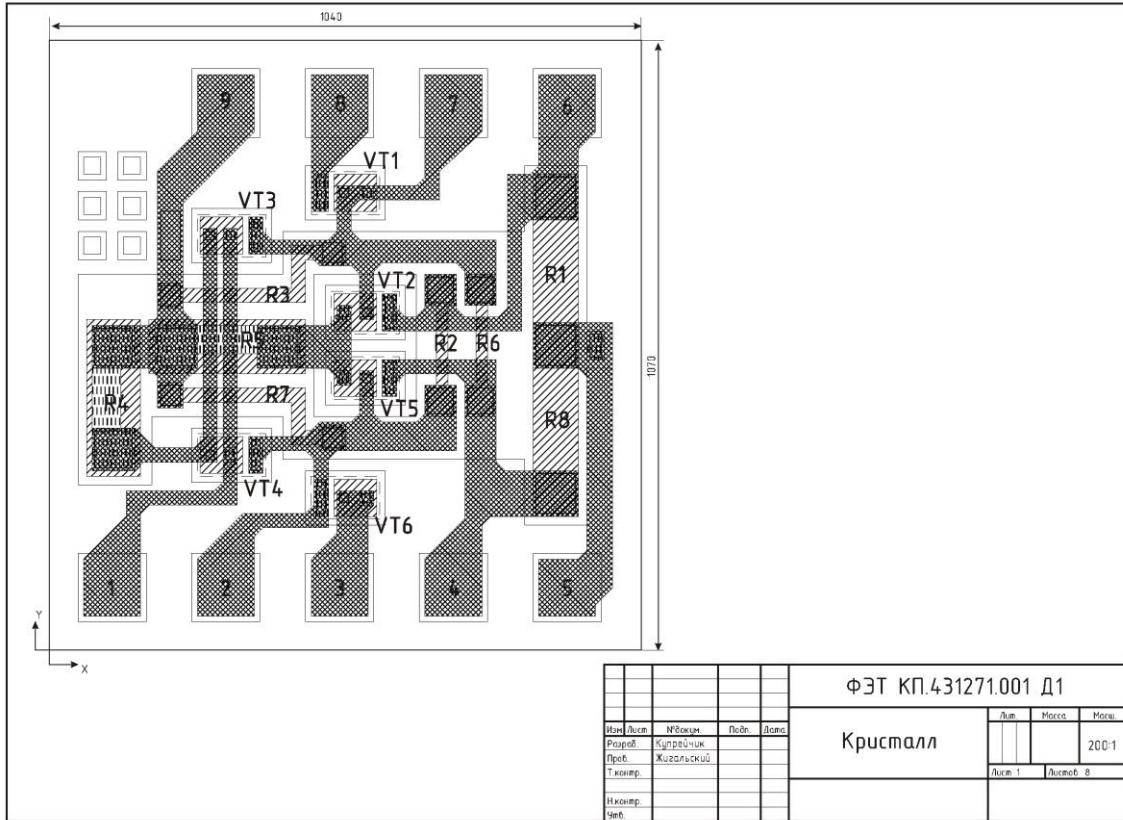

## Общий вид топологии

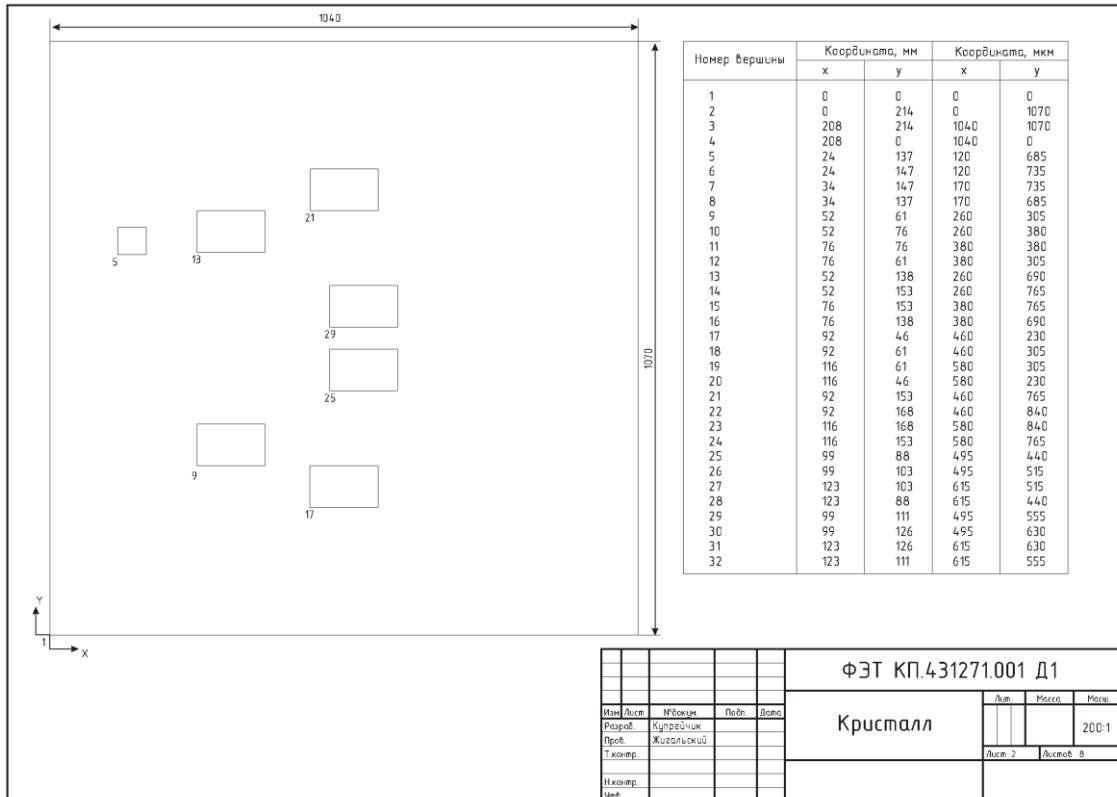

## Вид на скрытый слой

**ПРИЛОЖЕНИЕ 6**

**ПРИМЕР ОФОРМЛЕНИЯ ТИТУЛЬНОГО ЛИСТА**

**Министерство образования и науки Российской Федерации**

Т

ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ

УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР)

Кафедра физической электроники (ФЭ)

**ПРОЕКТИРОВАНИЕ ГИБРИДНОЙ ИНТЕГРАЛЬНОЙ

СХЕМЫ К238ХА5**

Пояснительная записка к курсовому проекту по дисциплине

«Проектирование и конструирование интегральных схем»

ФЭ КП. XXXXXX.008 ПЗ

Студент гр. 315

\_\_\_\_\_ А. П. Петров

«\_\_\_\_» \_\_\_\_\_ 20 \_\_\_\_ г.

Руководитель проекта

доцент каф. ФЭ

\_\_\_\_\_ А. А. Жигальский

«\_\_\_\_» \_\_\_\_\_ 20 \_\_\_\_ г.

2018