## А. В. Шарапов

## **МИКРОЭЛЕКТРОНИКА**

### Федеральное агентство по образованию

# Томский государственный университет систем управления и радиоэлектроники

#### А. В. Шарапов

## **МИКРОЭЛЕКТРОНИКА**

#### Учебное пособие

Рекомендовано Сибирским региональным отделением учебно-методического объединения высшего профессионального образования для межвузовского использования в качестве учебного пособия по дисциплине «Микроэлектроника» для студентов специальности 210106.65 «Промышленная электроника»

Рецензенты: зав. кафедрой промышленной и медицинской электроники

Томского политехнического университета, д-р техн. наук

проф. Г.С. Евтушенко;

начальник отдела ФГУП «НПЦ «Полюс», д-р техн. наук

Ю.М. Казанцев

#### Шарапов А.В.

Микроэлектроника: Уч. пособие. – Томск: Томский государственный университет систем управления и радиоэлектроники, 2007 – 138 с.

Излагаются принципы построения и функционирования логических элементов, дешифраторов, мультиплексоров, сумматоров, цифровых компараторов, триггеров, счетчиков, регистров, микросхем памяти. Рассмотрены примеры синтеза цифровых устройств комбинационного типа и цифровых автоматов.

Пособие предназначено для студентов вузов радиоэлектронного профиля дневной, вечерней и заочной форм обучения, и содержит краткий конспект лекций, примеры решения задач, варианты творческих заданий и компьютерный лабораторный практикум по цифровой схемотехнике.

© А.В.Шарапов,

2007

© Томск, гос. ун-т систем управления и радиоэлектроники, 2007

## СОДЕРЖАНИЕ

| 1. | Введ  | ение                                                |

|----|-------|-----------------------------------------------------|

| 2. | Осно  | вные понятия микроэлектроники                       |

|    | 2.1.  | Виды сигналов                                       |

|    | 2.2.  | Классификация микросхем и их условные обозначения   |

| 3. | Мате  | матические основы цифровой электроники              |

|    | 3.1.  | Позиционные системы счисления                       |

|    | 3.2.  | Таблица истинности                                  |

|    | 3.3.  | Совершенная дизъюнктивная нормальная форма          |

|    |       | логических функций                                  |

|    | 3.4.  | Основные законы булевой алгебры                     |

|    | 3.5.  | Диаграммы Венна                                     |

|    | 3.6.  | Карты Карно                                         |

|    | 3.7.  | Этапы синтеза цифрового устройства                  |

|    | 3.8.  | Примеры синтеза цифровых устройств                  |

|    | 3.9.  | Мажоритарный логический элемент                     |

| 4. | Базов | вые логические элементы                             |

|    | 4.1.  | Классификация логических элементов                  |

|    | 4.2.  | Базовый элемент ТТЛ                                 |

|    | 4.3.  | Логический расширитель                              |

|    | 4.4.  | Элемент с открытым коллектором                      |

|    | 4.5.  | Элемент с Z-состоянием на выходе                    |

| Pe | комен | дации по применению элементов ТТЛ                   |

|    |       | элемент ТТЛШ                                        |

|    |       | схема ЭСЛ                                           |

| Ба | зовые | элементы КМОП                                       |

|    |       | ые характеристики логических элементов              |

|    |       | ы микросхем логических элементов                    |

| _  | -     | хемы на основе арсенида галлия                      |

|    |       | оовые устройства комбинационного типа               |

|    | 5.1.  | Шифратор                                            |

|    | 5.2.  | Дешифратор                                          |

|    | 5.3.  | Преобразователи двоичного кода в двоично-десятичный |

|    |       | и наоборот                                          |

|    | 5.4.  | Дешифратор для управления 7-сегментным индикатором  |

|    | 5.5.  | Преобразователи кода Грея                           |

|    | 5.6.  | Мультиплексор                                       |

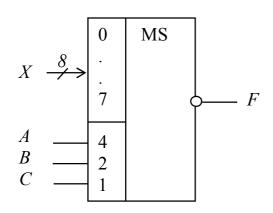

|    | 5.7.  | Реализация булевых функций с помощью                |

|    | J.1.  | мультиплексора                                      |

|    | 5.8.  | Двоичный сумматор                                   |

|    | 5.9.  | Двоично-десятичный сумматор                         |

|    | 5.10. | Схемы вычитания                                 | 62  |

|----|-------|-------------------------------------------------|-----|

|    | 5.11. | Преобразователь прямого кода в дополнительный   | 64  |

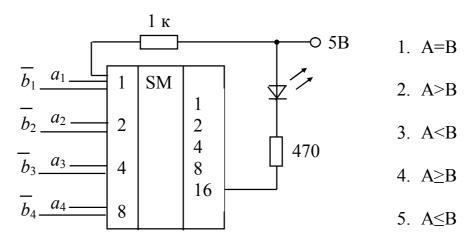

|    |       | Цифровые компараторы                            | 65  |

|    |       | Контроль четности                               | 66  |

|    |       | Примеры построения комбинационных цифровых уст- |     |

|    |       | ройств                                          | 67  |

| 6. | Цифро | овые устройства последовательностного типа      | 71  |

|    | 6.1.  | Классификация триггеров                         | 71  |

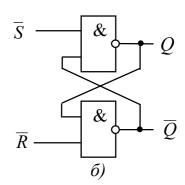

|    | 6.2.  | Асинхронный RS-триггер                          | 72  |

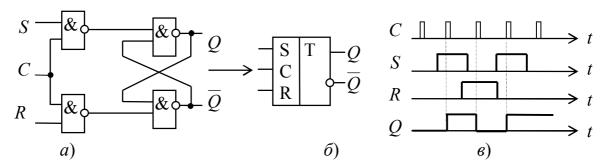

|    | 6.3.  | Тактируемый RS-триггер                          | 72  |

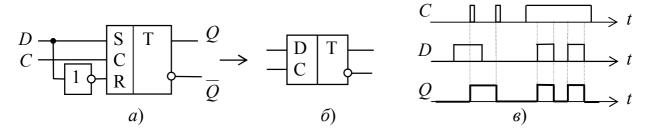

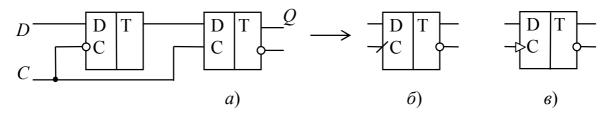

|    | 6.4.  | <b>D-триггеры</b>                               | 73  |

|    | 6.5.  | Т-триггер                                       | 74  |

|    | 6.6.  | ЈК-триггер                                      | 74  |

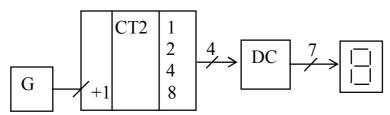

|    | 6.7.  | Классификация счетчиков                         | 76  |

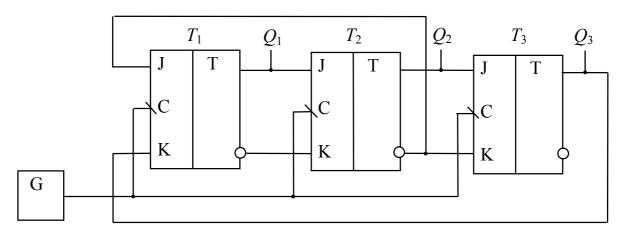

|    | 6.8.  | Асинхронный двоичный счетчик                    | 76  |

|    | 6.9.  | Асинхронный двоично-десятичный счетчик          | 77  |

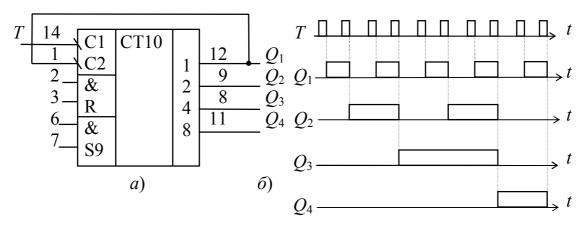

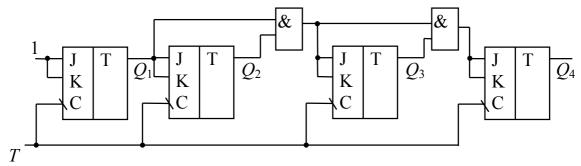

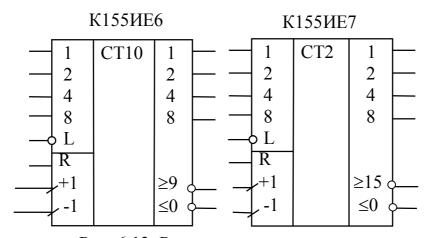

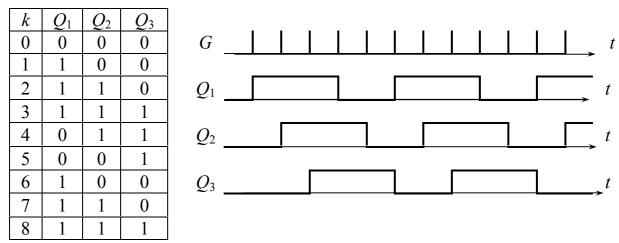

|    | 6.10. | Синхронный двоичный счетчик                     | 78  |

|    |       | Реверсивные счетчики                            | 78  |

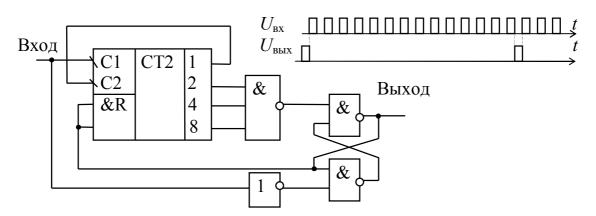

|    |       | Счетчики с произвольным модулем счета           | 79  |

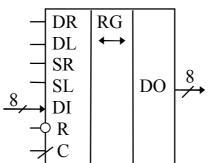

|    |       | Регистры сдвига                                 | 82  |

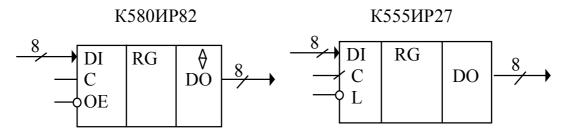

|    |       | Регистры памяти                                 | 82  |

|    |       | Универсальные регистры                          | 83  |

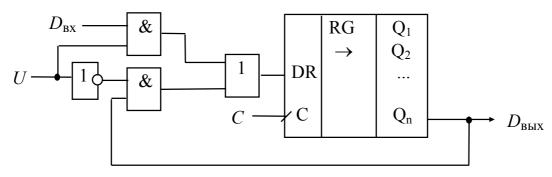

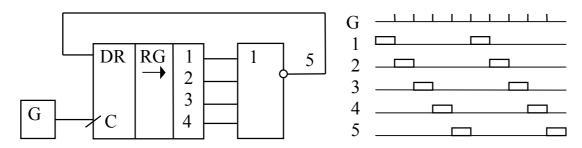

|    |       | Кольцевой регистр                               | 83  |

|    |       | Кольцевой счетчик                               | 84  |

|    |       | Счетчики на регистрах сдвига                    | 85  |

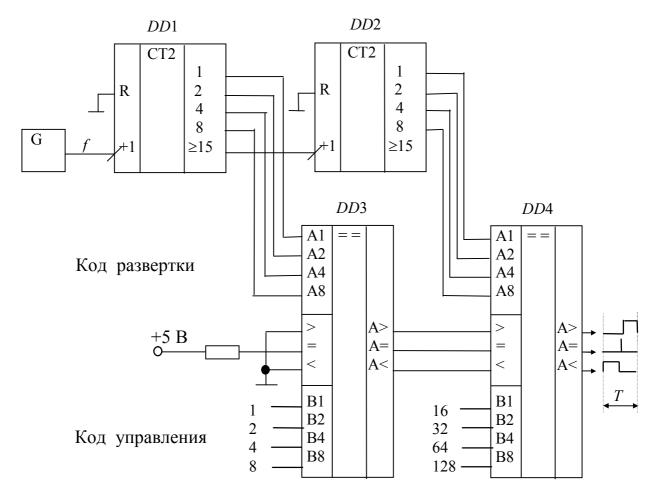

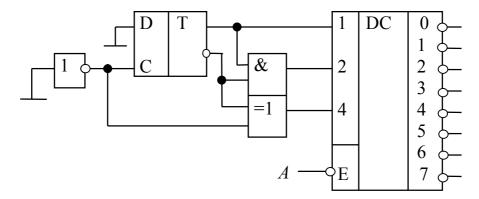

|    |       | Примеры построения цифровых устройств           |     |

|    |       | последовательностного типа                      | 86  |

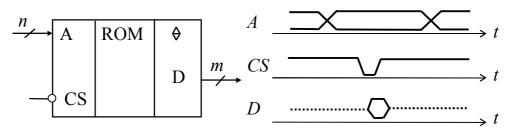

| 7. | Полуп | проводниковые запоминающие устройства           | 91  |

|    | 7.1.  | Классификация запоминающих устройств            | 91  |

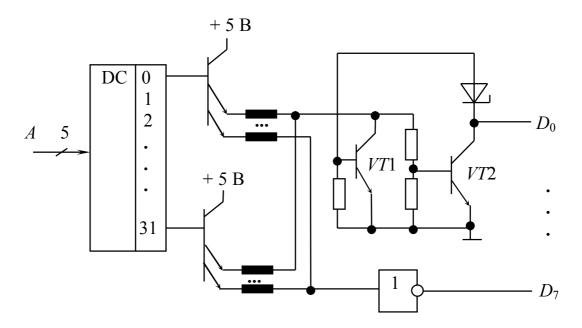

|    | 7.2.  | ПЗУ масочного типа                              | 92  |

|    | 7.3.  | Однократно программируемые ПЗУ                  | 93  |

|    | 7.4.  | Перепрограммируемые ПЗУ                         | 94  |

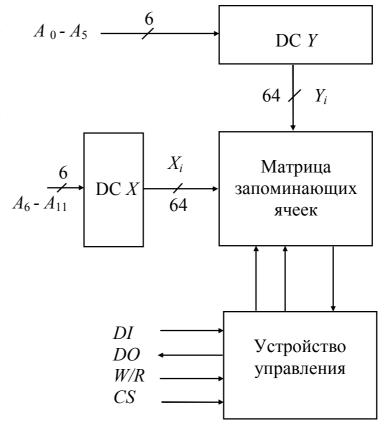

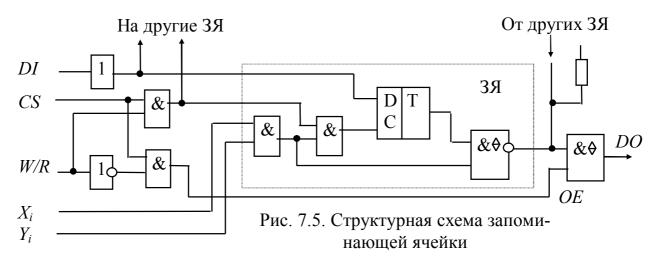

|    | 7.5.  | ОЗУ статического типа                           | 95  |

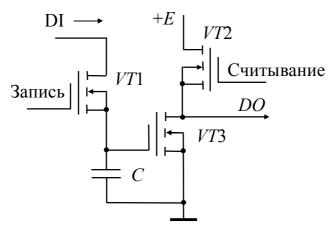

|    | 7.6.  | ОЗУ динамического типа                          | 96  |

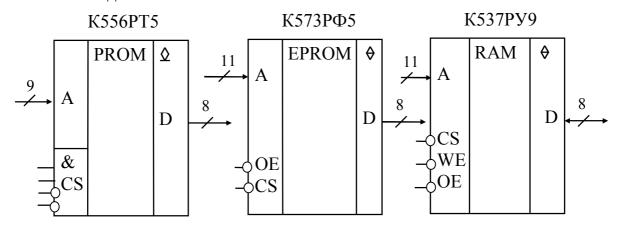

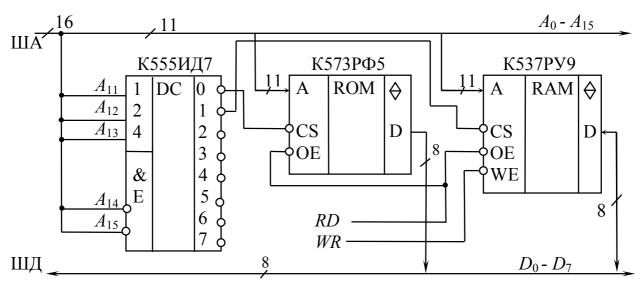

|    | 7.7.  | Примеры микросхем памяти                        | 97  |

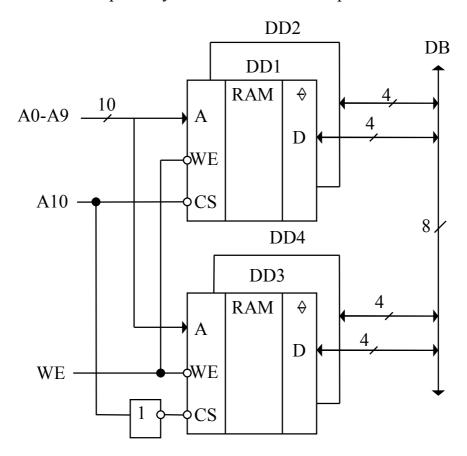

|    | 7.8.  | Организация блока памяти                        | 98  |

| 8. | Прим  | еры решения задач                               | 99  |

|    | _     | ъютерный практикум по цифровой схемотехнике     | 111 |

|    |       | нты творческих заданий                          | 124 |

|    | _     | ер выполнения творческого задания               | 127 |

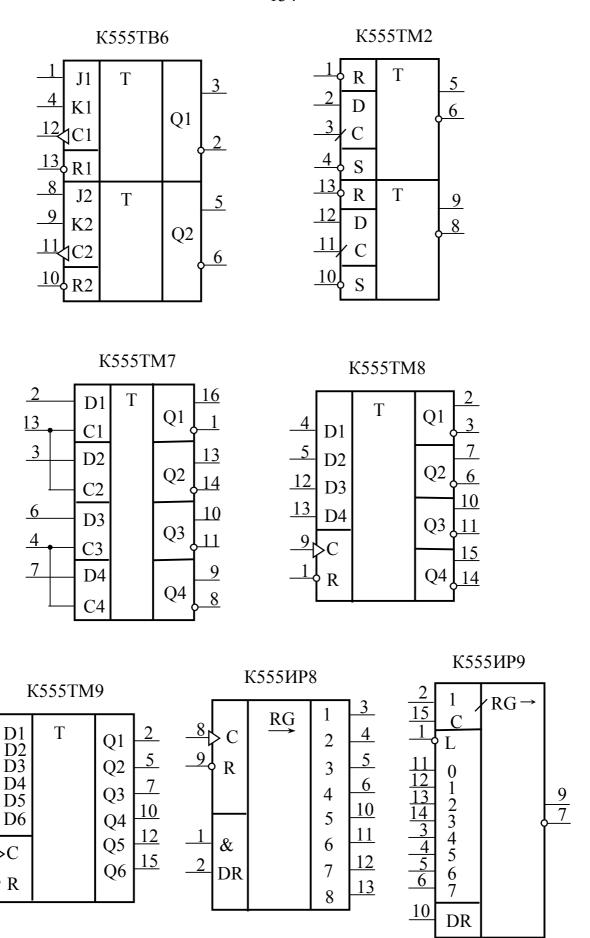

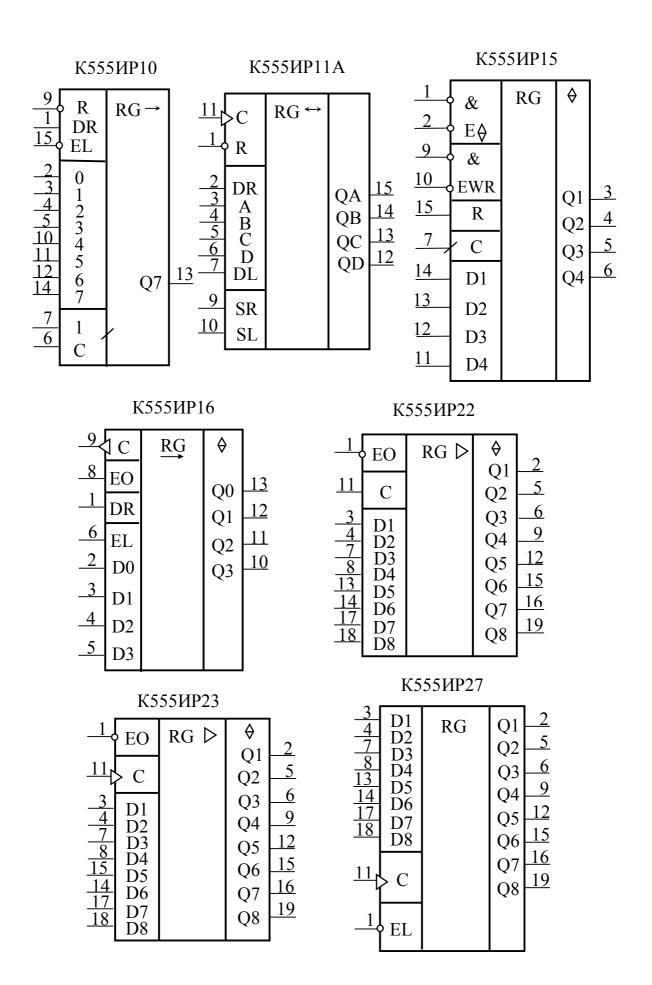

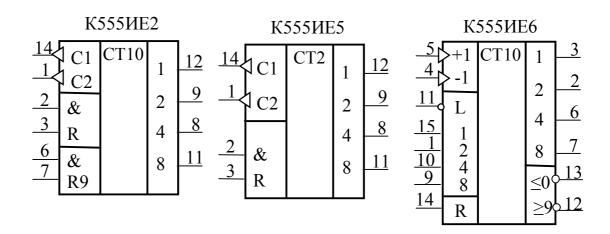

|    | -     | ние. Условные графические обозначения микросхем | 130 |

| _  |       | rpa                                             | 137 |

#### 1. ВВЕДЕНИЕ

Электроникой называют раздел науки и техники, занимающийся:

- исследованием физических явлений и разработкой приборов, действие которых основано на протекании электрического тока в твердом теле, вакууме или газе;

- изучением электрических свойств, характеристик и параметров названных приборов;

- практическим применением этих приборов в различных устройствах и системах.

Первое из указанных направлений составляет область физической электроники. Второе и третье направления составляют область технической электроники.

Схемотехника электронных устройств — это инженерное воплощение принципов электроники для практической реализации электронных схем, призванных выполнять конкретные функции генерирования, преобразования и хранения сигналов, несущих информацию в слаботочной электронике и функции преобразования энергии электрического тока в сильноточной электронике.

Исторически электроника явилась следствием возникновения и быстрого развития *радиотехники*. Радиотехнику определяют как область науки и техники, занимающуюся исследованиями, разработкой, изготовлением и применением устройств и систем, предназначенных для передачи информации по радиочастотным каналам связи.

У истоков радиотехники лежат научные открытия XIX века: работы М. Фарадея (англ.), выяснившего закономерности взаимодействия электрического и магнитных полей; Дж. Максвелла (англ.), обобщившего элементарные законы электромагнетизма и создавшего систему уравнений, описывающих электромагнитное поле. Дж. Максвелл теоретически предсказал новый вид электромагнитных явлений — электромагнитные волны, распространяющиеся в пространстве со скоростью света. Г. Герц (нем.) экспериментально подтвердил существование электромагнитных волн.

Первый радиоприемник был изобретен, сконструирован и успешно испытан в 1895 г. А.С. Поповым (рус.). Годом позже радиосвязь осуществил Г. Маркони (итал.), запатентовавший свое изобретение и ставший Нобелевским лауреатом в 1909 году.

С этих пор развитие радиотехники определялось развитием ее элементной базы, которая в основном определяется достижениями электроники. Интересно вкратце проследить за основными этапами развития ее элементной базы.

Простейший электронный прибор – вакуумный диод – был изобретен Т. Эдиссоном (амер.) в 1883 г., который вмонтировал металлический

электрод в баллон электрической лампы накаливания и зарегистрировал ток одного направления во внешней цепи. В 1904 г. Дж. Флемминг (англ.) впервые применил вакуумный диод в качестве детектора в радиоприемнике. Усилительный электровакуумный прибор – триод – был изобретен Луи де Форестом (амер.) в 1906 г. С этих пор в течение первой четверти ХХ столетия в ряде научных лабораторий многих стран мира происходило медленное созревание технологий электровакуумных приборов. В России это направление возглавил руководитель Нижегородской лаборатории М.А. Бонч-Бруевич. Уже в 1922 г. сотрудники этой лаборатории построили в Москве первую в мире радиовещательную станцию им. Коминтерна мощностью 12 кВт. А к 1927 г. было построено 57 таких станций. В 1925 г. была создана генераторная лампа мощностью 100 кВт. В 1933 г. в России вступила в строй мощнейшая в мире (500 кВт) радиостанция. Первый телевизионный передатчик мощностью 15 кВт введен в строй в Москве в 1948 г. А.И. Берг в 1927-1929 гг. создал классическую теорию передатчиков. В.А. Котельниковым в период с 1933 по 1946 гг. доказана теорема квантования по времени, заложившая основу цифровых методов обработки сигналов, показана возможность радиосвязи на одной боковой полосе и опубликована теория потенциальной помехоустойчивости.

Период с 1920 по 1955 гг. был эрой ламповой электроники.

Первый полупроводниковый триод — транзистор — создан в 1948 г. Дж. Бардиным и У. Браттейном (амер.). С 1955 г. начинается эра полупроводниковой электроники. Первые интегральные схемы появились в 1960-е годы. Первый микропроцессор датируется 1971 г.

В 1998 году транзистор отметил свой полувековой юбилей — в последний июньский день 1948 года американская фирма «Bell telephon laboratoris» продемонстрировала общественности только что изобретенный электронный прибор, о котором назавтра «Нью-Йорк Таймс» сообщила буднично и без пафоса: «Рабочие элементы прибора состоят из двух тонких проволочек, прижатых к кусочку полупроводникового вещества... Вещество усиливает ток, подводимый к нему по одной проволочке, а другая проволочка отводит усиленный ток. Прибор под названием «транзистор» в некоторых случаях можно использовать вместо электронных ламп».

Да, именно так выглядел первый транзистор, и неудивительно, что даже специалисты не сразу смогли разглядеть его триумфальное будущее. А между тем представленный прибор мог усиливать и генерировать электрические сигналы, а также выполнять функцию ключа, по команде открывающего или запирающего электрическую цепь. И, что принципиально важно, все это осуществлялось внутри твердого кристалла, а не в вакууме, как это происходит в электронной лампе. Отсюда следовал целый набор потенциальных достоинств транзистора: малые габариты, механическая прочность, высокая надежность, принципиально неограниченная долговечность.

Через три-четыре года, когда были разработаны значительно более совершенные конструкции транзисторов, все эти ожидаемые достоинства начали становиться реальностью.

Честь открытия транзисторного эффекта, за которое в 1956 году была присуждена Нобелевская премия по физике, принадлежит У. Шокли, Дж. Бардину, У. Браттейну. Характерно, что все трое были блистательными физиками, целенаправленно шедшими к этому открытию. Шокли, руководитель группы исследователей, еще в предвоенные годы читал лекции по квантовой теории полупроводников и подготовил фундаментальную монографию, которая надолго стала настольной книгой для специалистов в этой области. Высочайшая квалификация Бардина как физика-теоретика подтверждена не только изобретением транзистора и предсказанием ряда эффектов в поведении полупроводников, но и тем, что позднее, в 1972 году, совместно с двумя другими исследователями он был повторно удостоен Нобелевской премии — теперь за создание теории сверхпроводимости. Браттейн, самый старший в группе, к моменту изобретения транзистора имел за плечами пятнадцатилетний опыт исследования поверхностных свойств полупроводников.

Хотя само открытие транзисторного эффекта явилось до некоторой степени счастливой случайностью (говоря сегодняшним языком, они пытались изготовить *полевой* транзистор, а изготовили *биполярный*), теоретическая подготовка исследователей позволила им практически мгновенно осознать открытое и предсказать целый ряд гораздо более совершенных устройств. Иными словами, создание транзистора оказалось под силу лишь физикам, которые по необходимости владели еще и минимумом изобретательских навыков.

У нас в стране транзистор был воспроизведен в 1949 году во фрязинской лаборатории, возглавляемой А.В. Красиловым, крупным ученым, обладающим широчайшей эрудицией.

Первые транзисторы изготавливались на основе полупроводника *германия* и допускали рабочую температуру лишь до 70°C, а этого во многих прикладных задачах было недостаточно.

Во второй половине пятидесятых годов в развитии транзисторов произошел решающий качественный скачок: вместо германия стали использовать другой полупроводник — кремний. В итоге рабочая температура транзисторов выросла до 120-150°С, при этом их характеристики сохраняли высокую стабильность, а срок службы приборов стал практически бесконечным. Но, пожалуй, главное заключалось в том, что в 1959 году американской фирмой «Firechild» применительно к кремнию была разработана так называемая планарная технология. Принципиальным здесь было то, что тончайшая пленка диоксида кремния, выращенная при высокой температуре на поверхности кристалла,

надежно защищает кремний от агрессивных воздействий и является отличным изолятором. В этой пленке создают «окна», через которые, также при высокой температуре, в полупроводник вводят легирующие добавки — так изготавливаются фрагменты будущего прибора. Затем на изолированную от объема поверхность напыляют тонкопленочные алюминиевые токоподводы к активным зонам — и транзистор готов. Особенностями процесса является то, что все воздействия на пластину осуществляются в одной плоскости и что обеспечивается одновременная обработка тысяч и миллионов транзисторов на пластине, а это ведет к высочайшей степени воспроизводимости изделий и высокой производительности.

Методами планарной технологии легко обеспечить изоляцию транзисторов от подложки и друг от друга, а отсюда лишь шаг до создания *интегральной схемы* (*микросхемы*), т.е. создания электронной схемы с активными и пассивными компонентами и их соединениями на едином кристалле в едином технологическом процессе. Этот шаг был сделан в том же 1959 году. Мир вступил в эру *микроэлектроники*.

Типичная микросхема представляет собой кремниевый кристаллик (чип), в приповерхностной области которого изготовлено множество транзисторов, соединенных между собой пленочными алюминиевыми дорожками в заданную электрическую схему. В первой микросхеме «множество» состояло всего лишь из 12 транзисторов, но уже через два года уровень интеграции превысил 100 элементов на чипе, а к середине 60-х годов стали доминировать большие интегральные схемы (БИС), содержащие тысячи элементов, затем — сверхбольшие (СБИС) и т.д.

Микросхема обладает тем большей информационной мощностью, чем большее количество транзисторов она содержит, т.е. чем выше *пломность интеграции* (плотность упаковки активных элементов в кристалле). А она определяется минимальными размерами активного элемента и площадью кристалла, которые способна воспроизводить технология.

Изложенные в данном учебном пособии основы *цифровой схемо- техники* формируют схемотехнические навыки построения цифровых устройств на базе интегральных микросхем. Изучается принцип работы простейших логических элементов и методы проектирования на их основе преобразователей кодов, сумматоров, цифровых коммутаторов, триггеров, регистров, счетчиков, микросхем памяти. Проверить работу многих устройств можно путем компьютерного моделирования с помощью пакетов Electronics Workbench или Asimec.

Рекомендуемый список литературы включает прежде всего справочники по цифровым интегральным микросхемам. Из других источников, используемых в данном учебном пособии, хочется отметить работы доцентов ТУСУРа Потехина В.А. [12] и Шибаева А.А. [6], которым автор выражает искреннюю благодарность.

#### 2. ОСНОВНЫЕ ПОНЯТИЯ МИКРОЭЛЕКТРОНИКИ

#### 2.1. Виды сигналов

Назначение радиоэлектронных устройств, как известно, — получение, преобразование, передача и хранение информации, представленной в форме электрических сигналов. Сигналы, действующие в электронных устройствах, и соответственно сами устройства делят на две большие группы: аналоговые и цифровые.

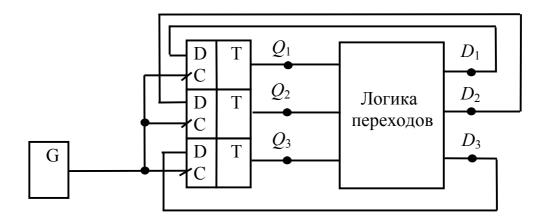

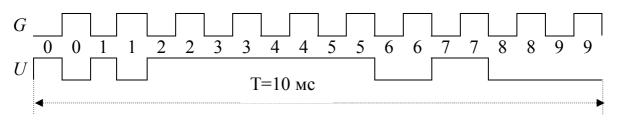

Рис. 2.1. Виды сигналов

Аналоговый сигнал — сигнал, непрерывный по уровню и во времени, т.е. такой сигнал существует в любой момент времени и может принимать любой уровень из заданного диапазона.

Квантованный сигнал — сигнал, который может принимать только определенные квантованные значения, соответствующие уровням квантования. Расстояние между двумя соседними уровнями — шаг квантования.

**Дискретизированный сигнал** — сигнал, значения которого заданы только в моменты времени, называемые моментами дискретизации. Расстояние между соседними моментами дискретизации — шаг дискретизации Td. При постоянном Td применима теорема Котельникова:  $\frac{1}{Td} = fd \ge 2fe$ , где fe— верхняя граничная частота спектра сигнала.

**Цифровой сигнал** — сигнал, квантованный по уровню и дискретизированный во времени. Квантованные значения цифрового сигнала обычно кодируются некоторым кодом, при этом каждый выделенный в процессе дискретизации отсчет заменяется соответствующим кодовым словом, символы которого имеют два

значения – 0 и 1.

Типичными представителями устройств аналоговой электроники являются устройства связи, радиовещания, телевидения. Общие требования, предъявляемые к аналоговым устройствам, — минимальные искажения. Стремление выполнить эти требования приводит к усложнению электрических схем и конструкции устройств. Другая проблема аналоговой электроники — достижение необходимой помехоустойчивости, ибо в аналоговом канале связи шумы принципиально неустранимы.

Цифровые сигналы формируются электронными схемами, транзисторы в которых либо закрыты (ток близок к нулю), либо полностью открыты (напряжение близко к нулю), поэтому на них рассеивается незначительная мощность и надежность цифровых устройств получается более высокой, чем аналоговых.

Цифровые устройства более помехоустойчивы, чем аналоговые, так как небольшие посторонние возмущения не вызывают ошибочного срабатывания устройств. Ошибки появляются только при таких возмущениях, при которых низкий уровень сигнала воспринимается как высокий или наоборот. В цифровых устройствах можно также применить специальные коды, позволяющие исправить ошибки. В аналоговых устройствах такой возможности нет.

Цифровые устройства нечувствительны к разбросу (в допустимых пределах) параметров и характеристик транзисторов и других элементов схем. Безошибочно изготовленные цифровые устройства не нужно настраивать, а их характеристики полностью повторяемы. Все это очень важно при массовом изготовлении устройств по интегральной технологии. Экономичность производства и эксплуатации цифровых интегральных микросхем привела к тому, что в современных радиоэлектронных устройствах цифровой обработке подвергаются не только цифровые, но и аналоговые сигналы. Распространены цифровые фильтры, регуляторы, перемножители и др. Перед цифровой обработкой аналоговые сигналы преобразуются в цифровые с помощью аналого-цифровых преобразователей (АЦП). Обратное преобразование — восстановление аналоговых сигналов по цифровым — выполняется с помощью цифроаналоговых преобразователей (ЦАП).

При всем многообразии задач, решаемых устройствами цифровой электроники, их функционирование происходит в системах счисления, оперирующих всего двумя цифрами: нуль (0) и единица (1).

Работа цифровых устройств обычно *тактируется* достаточно высокочастотным генератором тактовых импульсов. В течение одного такта реализуется простейшая микрооперация — чтение, сдвиг, логическая команда и т.п. Информация представляется в виде цифрового слова. Для передачи слов используется два способа — параллельный и последователь-

ный. Последовательное кодирование применяется при обмене информацией между цифровыми устройствами (например, в компьютерных сетях, модемной связи). Обработка информации в цифровых устройствах реализуется при использовании параллельного кодирования информации, обеспечивающего максимальное быстродействие.

Элементную базу для построения цифровых устройств составляют интегральные микросхемы (ИМС), каждая из которых реализуется с использованием определенного числа логических элементов — простейших цифровых устройств, выполняющих элементарные логические операции.

#### 2.2. Классификация микросхем и их условные обозначения

Промышленностью выпускается широкая номенклатура интегральных микросхем различной степени интеграции. Кроме деления ИМС в зависимости от технологии изготовления (пленочные, гибридные, монолитные), ИМС делят на цифровые и аналоговые. Цифровые ИМС оперируют с напряжениями, принимающими только два возможных значения - логического нуля и логической единицы. Аналоговые ИМС могут работать с напряжениями, непрерывными по времени и значению. В зависимости от степени интеграции цифровые ИМС либо выполняют отдельные логические операции (например, И-НЕ или ИЛИ-НЕ), либо образуют целые узлы цифровых устройств (счетчики, регистры, микросхемы памяти, процессоры и т.д.). Аналоговые ИМС (операционные усилители, компараторы напряжений, таймеры, стабилизаторы постоянного напряжения) выполняют разнообразные функции: усиление сигналов, генерирование колебаний различной формы, модуляцию и демодуляцию сигналов и много других преобразований. Микросхемы, предназначенные для цифроаналогового (ЦАП) и аналого-цифрового преобразования сигналов (АЦП), относят к числу аналоговых.

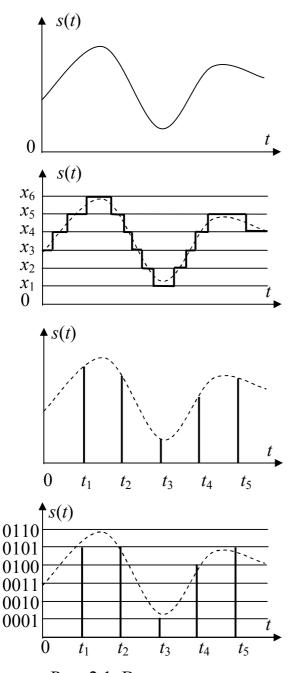

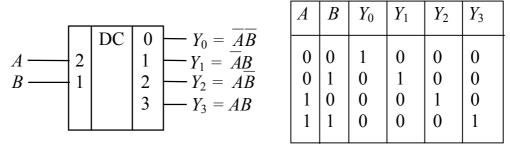

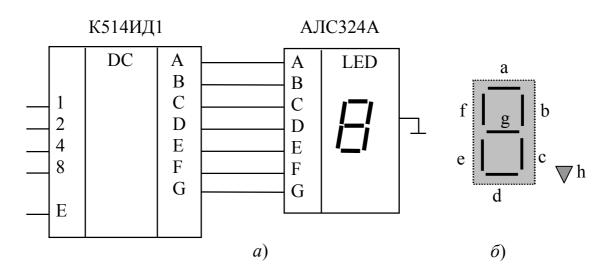

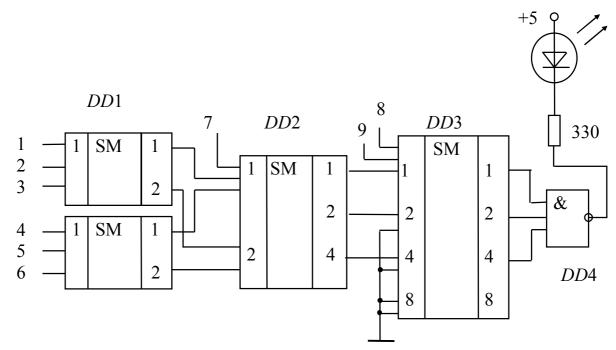

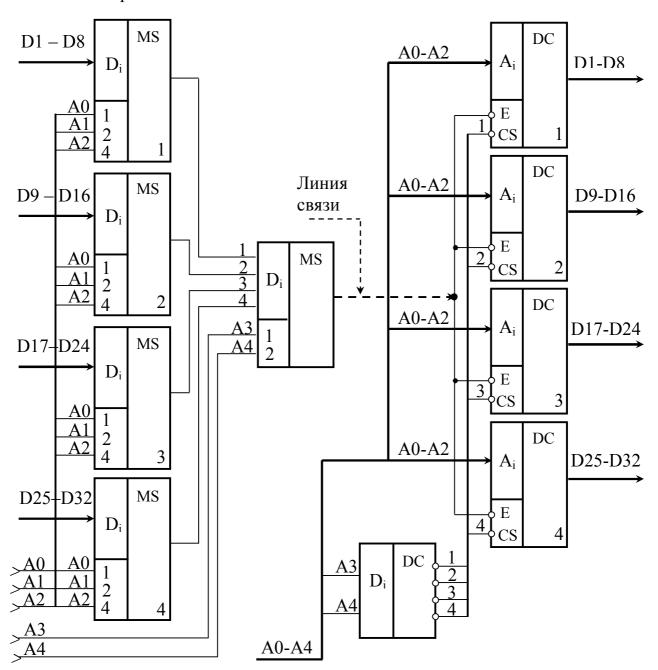

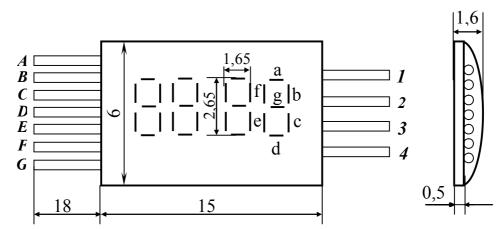

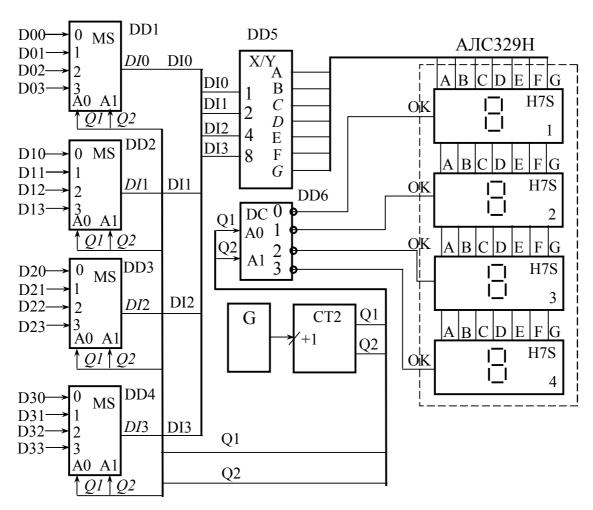

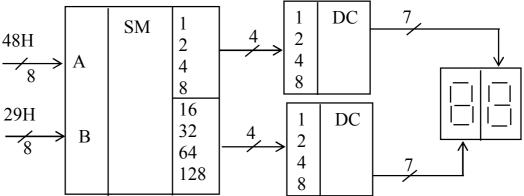

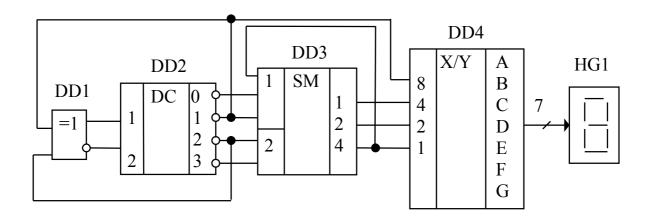

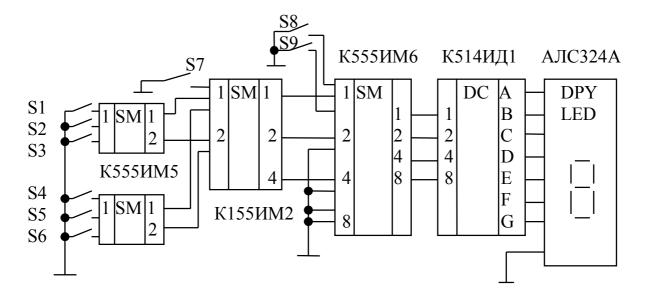

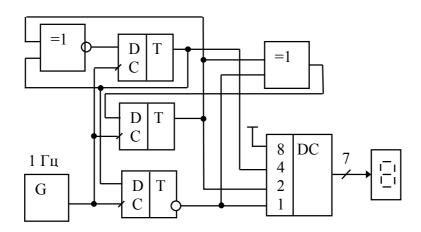

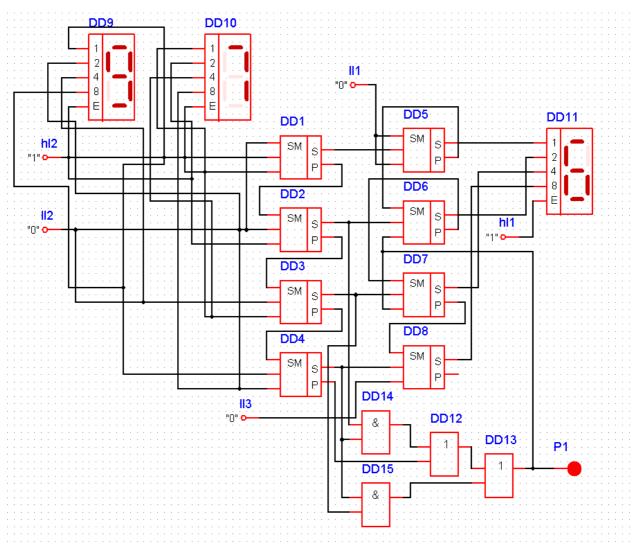

На функциональной схеме цифрового электронного термометра (диапазон температур от 0 до  $400^{\circ}$ C) к аналоговой части устройства относятся усилитель постоянного тока (УПТ) и 12-разрядный АЦП, к цифровой – преобразователь двоичного кода в двоично-десятичный (X/Y) и дешифратор DC, преобразующий этот код в код управления четырьмя цифровыми семисегментными индикаторами (рис. 2.2).

Рис. 2.2. Функциональная схема электронного термометра

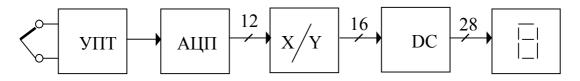

Стандартами установлена система условных обозначений микросхем. Большинство ИМС объединено в серии, которые включают ряд различных ИМС, согласованных по напряжению источников питания, уровням входных и выходных сигналов, входным и выходным сопротивлениям и конструктивно-технологическим особенностям. Серию стремятся разрабатывать так, чтобы из микросхем, входящих в нее, можно было создать законченные электронные устройства, хотя допускается использование в одном устройстве ИМС различных серий.

В принятой системе обозначений выпускаемые отечественной промышленностью ИМС делятся по конструктивно-технологическому исполнению на три группы:

- a) 1, 5, 6, 7 полупроводниковые (монолитные);

- б) 2, 4, 8 гибридные;

- в) 3 прочие (пленочные, керамические и др.).

Условное обозначение серии ИМС состоит из двух элементов: первый — цифра, обозначающая конструктивно-технологическую группу; второй — двух- или трехзначное число, указывающее порядковый номер серии. Например, серия, обозначенная числом 1533, принадлежит к полупроводниковым ИМС с порядковым номером серии 533.

По характеру выполняемых функций ИМС подразделяют на подгруппы: генераторы, усилители, триггеры, модуляторы и т.д. В свою очередь подгруппы делятся на виды. Например, подгруппа «Схемы цифровых устройств» включает в себя следующие виды ИМС: регистры, сумматоры, счетчики импульсов, дешифраторы и др. Обозначения подгрупп и видов стандартизованы. Например, буквы ИР в условном обозначении ИМС будут обозначать, что эта ИМС из подгруппы «Схемы цифровых устройств» относится к виду «регистры». В табл. 2.1 приведена неполная классификация видов ИМС.

Условное обозначение микросхемы состоит из трех- или четырехзначного обозначения серии микросхем, двух букв, означающих подгруппу и вид микросхемы, и порядкового номера разработки микросхемы.

Буквы (необязательные) К, КМ, КН, КР, и КА, стоящие в начале условного обозначения микросхемы, характеризуют условия ее приемки на заводе-изготовителе, причем буква К означает микросхемы широкого применения.

Для характеристики материала и типа корпуса перед цифровым обозначением серии могут быть добавлены следующие буквы:

Р – пластмассовый корпус типа ДИП (корпус с прямоугольными выводами, перпендикулярными плоскости основания корпуса и выходящими за пределы проекции тела корпуса на плоскость основания);

Таблица 2.1 Условные обозначения микросхем

| Подгруппа и вид ИМС        | Обо-     | Подгруппа и вид ИМС     | Обо-   |

|----------------------------|----------|-------------------------|--------|

| по функциональному         | значе-   | по функциональному      | значе- |

| назначению                 | ние      | назначению              | ние    |

| Формирователи:             | 11110    | Логические элементы:    |        |

| импульсов прямоугольной    |          | И–НЕ                    | ЛА     |

| формы                      | АΓ       | И–НЕ/ИЛИ–НЕ             | ЛБ     |

| прочие                     | АΠ       | расширители             | ЛД     |

| Схемы вычислительных       | 7 111    | или–не                  | ЛE     |

| средств:                   |          | И                       | ЛИ     |

| контроллеры                | ВВ       | Модуляторы:             | 7111   |

| микропроцессоры            | BM       | амплитудные             | MA     |

| специализированные         | ВЖ       | прочие                  | МП     |

| Генераторы:                | Dire     | Преобразователи:        | 14111  |

| прямоугольных сигналов     | ГГ       | цифроаналоговые         | ПА     |

| гармонических сигналов     | ГС       | аналого-цифровые        | ПВ     |

| Детекторы:                 | 10       | код-код                 | ПР     |

| амплитудные                | ДА       | Схемы запоминающих      | 111    |

| фазовые                    | ДФ       | устройств:              |        |

| прочие                     | ДП       | ПЗУ (масочные)          | PE     |

| Схемы источников           | <u> </u> | O3Y                     | РУ     |

| вторичного электропитания: |          | ПЗУ с УФ-стиранием      | РФ     |

| выпрямители                | ЕВ       | Схемы сравнения:        |        |

| стабилизаторы напряжения   |          | по напряжению           | CA     |

| импульсные                 | ЕК       | Триггеры                |        |

| стабилизаторы напряжения   |          | типа ЈК (универсальные) | ТВ     |

| непрерывные                | EH       | типа D (с задержкой)    | TM     |

| Схемы цифровых устройств:  | 211      | типа RS                 | TP     |

| АЛУ                        | ИА       | типа Т (счетные)        | TT     |

| шифраторы                  | ИВ       | Усилители:              |        |

| дешифраторы                | ИД       | операционные            | УД     |

| счетчики                   | ИЕ       | импульсных сигналов     | УЙ     |

| комбинированные            | ИК       | низкой частоты          | УН     |

| полусумматоры              | ИЛ       | высокой частоты         | УВ     |

| сумматоры                  | ИМ       | Многофункциональные     |        |

| прочие                     | ИП       | схемы:                  |        |

| регистры                   | ИР       | аналоговые              | XA     |

| Коммутаторы и ключи:       |          | цифровые                | ХЛ     |

| напряжения                 | КН       | комбинированные         | XK     |

| прочие                     | КП       | прочие                  | ХΠ     |

A – пластмассовый планарный корпус (прямоугольный корпус с выводами, расположенными параллельно плоскости основания и выходящими за пределы проекции его тела на плоскость основания);

М – металлокерамический корпус типа ДИП;

Е – металлополимерный корпус типа ДИП;

С – стеклокерамический корпус типа ДИП;

И – стеклокерамический планарный корпус;

H – керамический «безвыводной» корпус.

В условных обозначениях микросхем, выпускаемых в бескорпусном варианте, перед номером серии добавляют букву Б. Таким образом, бескорпусные аналоги обычной серии 155 обозначаются Б155.

Пример расшифровки обозначения микросхемы KP1533TM2 показан на рис. 2.3.

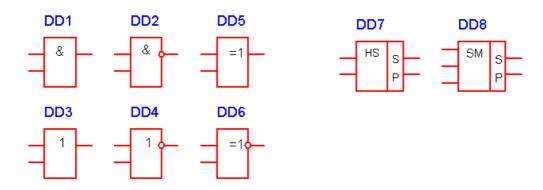

Рис. 2.3. Пример обозначения микросхемы

Если принципиальные схемы электронных устройств, использующих ИМС, выполнять, полностью отображая их внутреннюю структуру с помощью условных графических обозначений (УГО) составляющих компонентов, то схема получится очень громоздкой и не наглядной. Отображение на принципиальной схеме внутренней структуры ИМС становится своего рода избыточной информацией, затрудняющей составление и чтение схем. Разработчику электронной аппаратуры важно знать, из каких функциональных узлов можно создать то или иное устройство, а внутренняя структура узла зачастую его просто не интересует. Этим объясняется тот факт, что при составлении принципиальных схем цифровых и аналоговых устройств пользуются только обобщенными символами функциональных узлов.

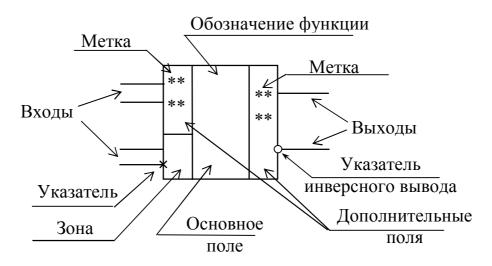

УГО элементов (узлов) аналоговой и цифровой техники строят на основе прямоугольника. В самом общем виде УГО может содержать основное и два дополнительных поля, расположенных по обе стороны от основного (рис. 2.4). Размер прямоугольника по ширине зависит от наличия дополнительных полей и числа помещенных в них знаков, по высоте — от числа выводов, интервалов между ними и числа строк информации в основном и

дополнительных полях. В основном поле указывают функциональное назначение элемента, а в дополнительных — метки, обозначающие функции или назначение выводов. В местах присоединения линий-выводов изображают специальные знаки (указатели), характеризующие их особые свойства (инверсные, динамические и т.д.). Группы выводов могут быть разделены увеличенным интервалом или помещены в обособленную зону. Согласно стандарту, ширина основного поля должна быть не менее 10 мм, дополнительных — не менее 5 мм, расстояние между выводами — 5 мм.

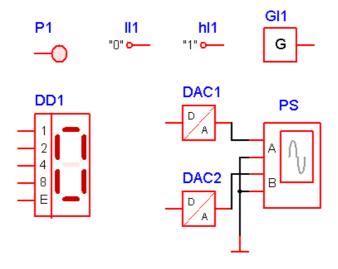

Рис. 2.4. УГО элементов аналоговой и цифровой техники

Выводы элементов схемы делятся на входы, выходы, двунаправленные выводы (служат как для ввода, так и для вывода информации) и выводы, не несущие информации (например, для подключения питания, внешних RC-цепей и т.п.). Входы изображают слева, выходы — справа, остальные выводы — с любой стороны УГО. При необходимости разрешается поворачивать обозначение на угол  $90^{\circ}$  по часовой стрелке, т.е. располагать входы сверху, а выходы снизу.

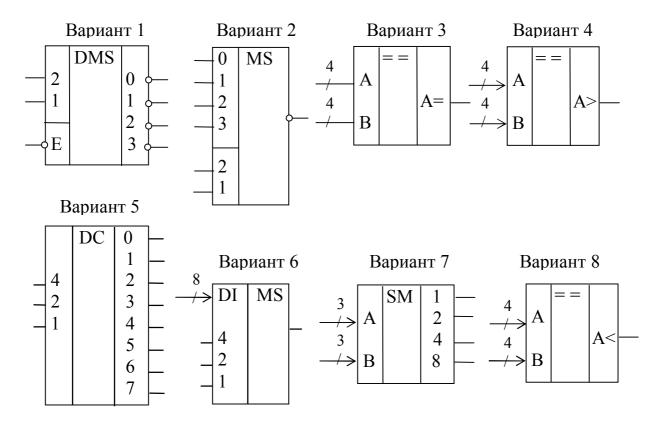

Функциональное назначение элемента указывают в верхней части основного поля УГО. Его составляют из прописных букв латинского алфавита, арабских цифр и специальных знаков, записываемых без пробелов. Примеры обозначений основных функций приведены в табл. 2.2. Сложные функции образуют из простых, располагая их в последовательности обработки сигнала.

Назначение выводов указывают метками, помещаемыми напротив них в дополнительных полях. Как и обозначения функций элементов, они могут состоять из букв латинского алфавита, арабских цифр и специальных знаков. Например, вывод установки ИМС в состояние «1» обозначается как S (Set), а сброс схемы в нулевое состояние – как R (Reset).

| Таблица 2.2                               |                      |  |  |  |  |

|-------------------------------------------|----------------------|--|--|--|--|

| Примеры функциональных об                 | бозначений ИС        |  |  |  |  |

| Функция                                   | Обозначение          |  |  |  |  |

| Память                                    | M                    |  |  |  |  |

| Оперативное запоминающее устройство (ОЗУ) | RAM                  |  |  |  |  |

| Постоянное запоминающее                   | ROM                  |  |  |  |  |

| устройство (ПЗУ) Логическое И             | & KOWI               |  |  |  |  |

| Регистр:                                  | a a                  |  |  |  |  |

| общее обозначение                         | RG                   |  |  |  |  |

| со сдвигом слева направо                  | $RG \rightarrow$     |  |  |  |  |

| с реверсивным сдвигом                     | $RG \leftrightarrow$ |  |  |  |  |

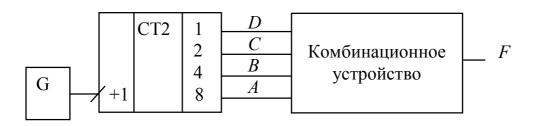

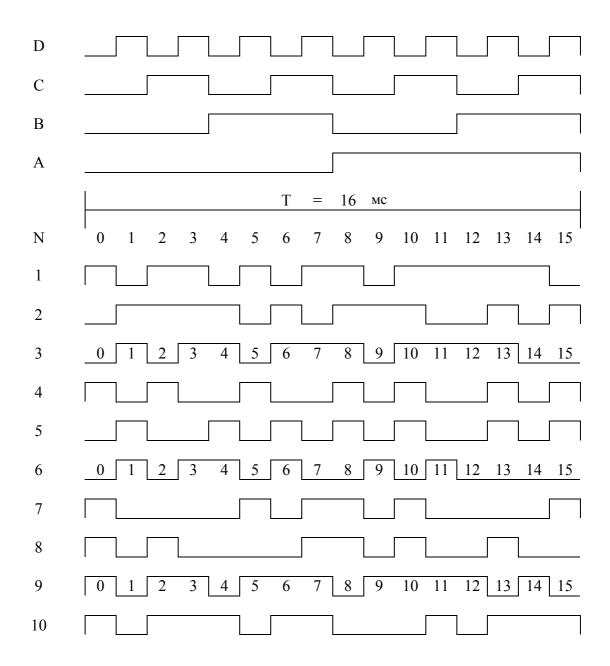

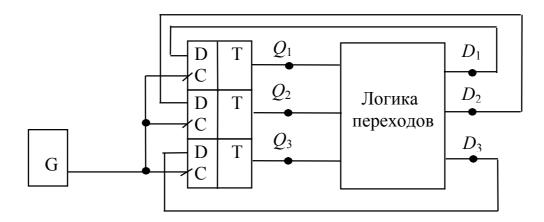

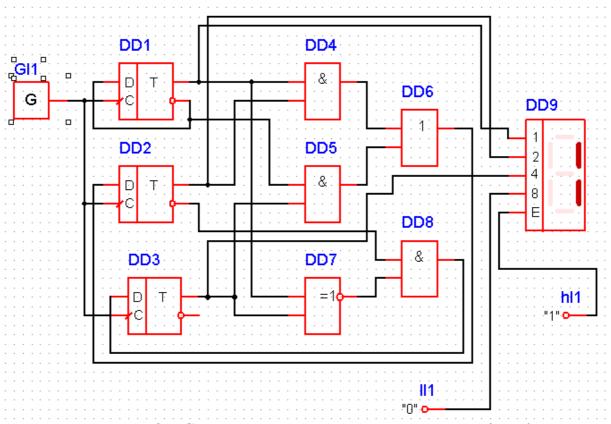

| Счетчик двоичный                          | CT2                  |  |  |  |  |

| Счетчик десятичный                        | CT10                 |  |  |  |  |

| Триггер:                                  |                      |  |  |  |  |

| общее обозначение                         | T                    |  |  |  |  |

| двухступенчатый                           | TT                   |  |  |  |  |

| Набор резисторов                          | *R                   |  |  |  |  |

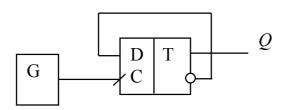

| Генератор                                 | G                    |  |  |  |  |

| Компаратор (сравнение)                    | ==                   |  |  |  |  |

| Усилитель                                 | $\triangleright$     |  |  |  |  |

| Преобразователь цифро-<br>аналоговый      | #/^                  |  |  |  |  |

| Преобразователь аналого-<br>цифровой      | ^/#                  |  |  |  |  |

Выводы ИМС могут быть помечены указателями, определяющими их статические и динамические свойства. Указатели проставляют на линии контура УГО или на линии связи около линии контура УГО со стороны линии вывода. Прямые статические выводы изображают линиями, присоединенными к основному или дополнительным полям УГО без каких-либо знаков, инверсные — в виде кружка на конце. Отличительный признак динамического вывода — указатель в виде косой черточки, стрелки или треугольника. Выводы, не несущие логической информации, выделяют крестиком, который наносят либо в месте присоединения к УГО (рис. 2.4), либо в непосредственной близости от него.

По функциональному назначению в цифровых ИМС выделяют следующие устройства.

**Погические элементы** — это ИМС, реализующие базовые логические функции НЕ, И, ИЛИ и их комбинации И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ. Часть ЛЭ, помимо логических операций, выполняет функции усилителей мощности.

**Драйверы.** Драйверами принято считать ИМС с повышенной нагрузочной способностью, основным назначением которых является организация связи с периферийными устройствами.

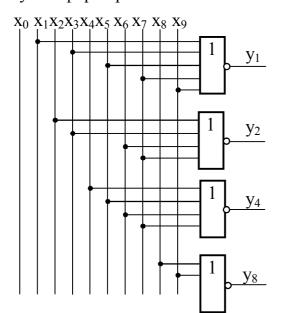

**Шифраторы.** Назначение шифратора – преобразование входного *унитарного* кода в натуральный двоичный.

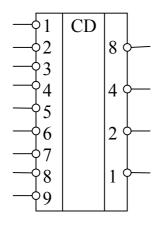

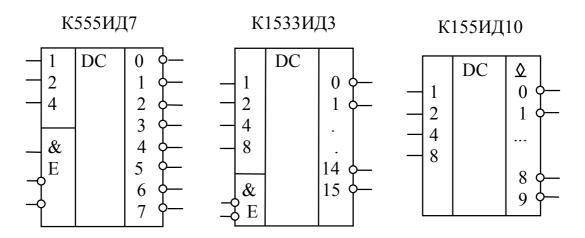

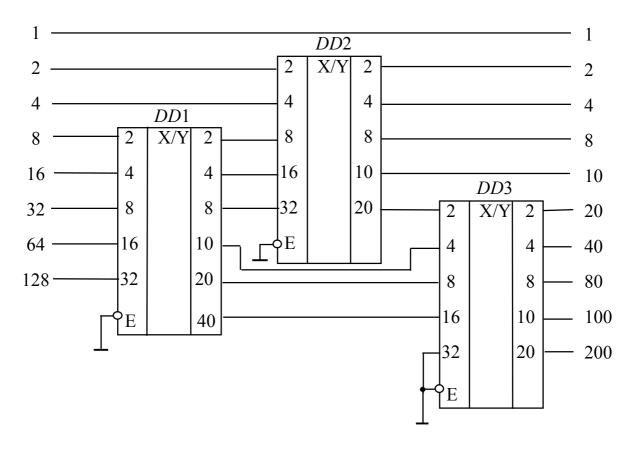

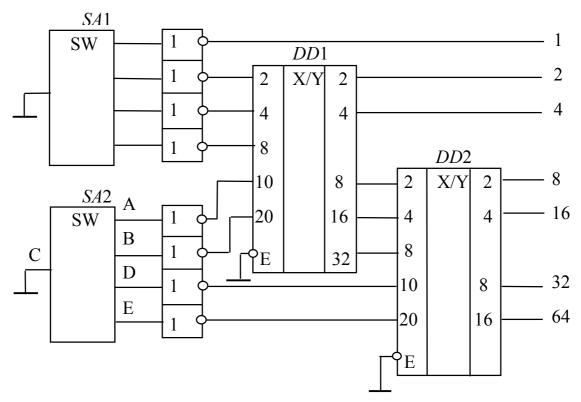

**Дешифраторы** выполняют функции обратные шифраторам, т.е. преобразуют двоичный код в унитарный. К специальным дешифраторам относятся преобразователи двоичного кода в коды управления знакосинтезирующими индикаторами.

${\it Мультиплексоры}$  направляют один из m входных сигналов на  $o\partial uh$  выход.

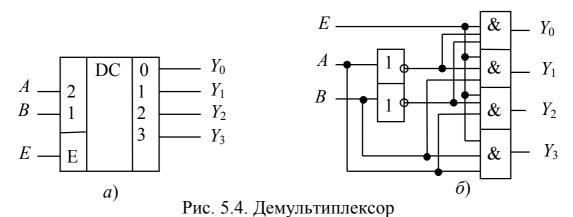

**Демультииллексоры** решают обратную задачу — направляют *один* входной сигнал в один из m выходных каналов.

Арифметическими устройствами являются сумматоры двоичных чисел, умножители двоичных чисел, AЛУ — арифметическо-логические устройства, схемы контроля четности, преобразователи двоичных кодов, иифровые компараторы (устройства сравнения двоичных чисел).

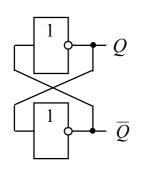

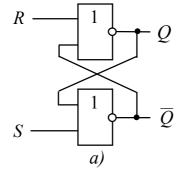

*Триггеры* – устройства, служащие для *запоминания* логических состояний.

**Регистры**. Регистром называется триггерная линейка, служащая для записи, хранения, сдвига и вывода информации.

**Счетчики** числа импульсов — суммирующие, вычитающие, реверсивные. Счетчики могут выполнять роль программируемых *делителей* частоты.

**Релаксационные** устройства — типа мультивибраторов и одновибраторов.

Запоминающие устройства предназначены для записи, хранения и выдачи информации.

Степень интеграции (показатель сложности) ИС оценивается числом элементов, размещенных на одном кристалле или подложке:

малая интегральная схема (МИС) — до 100; средняя интегральная схема (СИС) — 101 –1000; большая интегральная схема (БИС) — 1001 – 10000; сверхбольшая интегральная схема (СБИС) — свыше 100000.

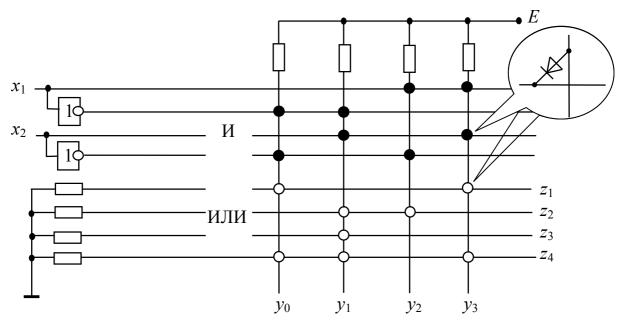

Все цифровые устройства можно отнести к одному из двух основных классов: комбинационные (без памяти) и последовательностные (с памятью). *Комбинационными* называют устройства, состояние выходов которых в любой момент времени однозначно определяется значениями вход-

ных переменных в тот же момент времени. Это логические элементы, преобразователи кодов (в том числе шифраторы и дешифраторы), распределители кодов (мультиплексоры и демультиплексоры), компараторы кодов, арифметико-логические устройства (сумматоры, вычитатели, умножители, собственно АЛУ), постоянные запоминающие устройства (ПЗУ), программируемые логические матрицы (ПЛМ).

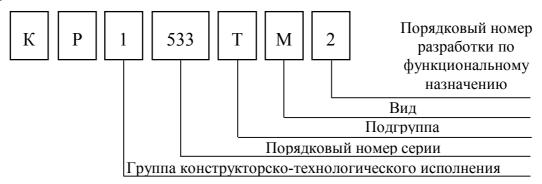

Выходное состояние *последовательностиюго* цифрового устройства (конечного автомата) в данный момент времени определяется не только логическими переменными на его входах, но еще зависит и от порядка (последовательности) их поступления в предыдущие моменты времени. Иными словами, конечные автоматы должны обязательно содержать элементы памяти, отражающие всю предысторию поступления логических сигналов, и выполняются на триггерах, в то время как комбинационные цифровые устройства могут быть целиком построены только на логических элементах. К числу цифровых устройств последовательностного типа относят триггеры, регистры, счетчики, оперативные запоминающие устройства (ОЗУ), микропроцессорные устройства (микропроцессоры и микроконтроллеры).

#### **Пример 2.1.** В приведенном списке ИМС указать:

- а) цифровые интегральные микросхемы комбинационного типа;

- б) микросхемы, выполненные по гибридной технологии;

- в) цифровые интегральные микросхемы последовательностного типа.

| К1533ИЕ6 | К155КП7  |

|----------|----------|

| К555ИР1  | K556PT5  |

| К140УД6  | K561TM2  |

| К252ПА1  | К564 ИМ3 |

| 301HP1A  | К537РУ8  |

| K142 EH5 | К133ЛА3  |

Решение. К числу комбинационных ИМС в приведенном списке относятся логический элемент К133ЛА3, мультиплексор К155КП7, сумматор К564 ИМ3, постоянное запоминающее устройство К556РТ5. По гибридной технологии выполнена микросхема цифроаналогового преобразователя К252ПА1, номер серии которой начинается с цифры 2. К числу последовательностных ИМС относятся триггер К561ТМ2, регистр К555ИР1, счетчик К1533ИЕ6, оперативное запоминающее устройство К537РУ8. Кроме перечисленных микросхем в данном списке приведены операционный усилитель К140УД6, стабилизатор напряжения К142ЕН5, набор резисторов 301НР1А, которые относятся к аналоговым ИМС, причем последняя микросхема выполнена по пленочной технологии (номер серии начинается с цифры 3).

#### 3. МАТЕМАТИЧЕСКИЕ ОСНОВЫ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

#### 3.1. Позиционные системы счисления

Системой счисления называют способ изображения произвольного числа ограниченным набором символов, называемых цифрами. Номер позиции, определяющий вес, с которым данная цифра складывается в числе, называют разрядом, а системы счисления, обладающие отмеченным свойством, – позиционными.

В общем случае n-разрядное положительное число N в произвольной системе счисления с основанием p представляется суммой вида

$$N = \sum_{k=0}^{n-1} a_k p^k,$$

(3.1)

где  $a_k$  - отдельные цифры в записи числа, значения которых равны членам натурального ряда в диапазоне от 0 до (p-1).

При выполнении вычислений цифровыми электронными устройствами используются элементы с двумя устойчивыми состояниями. По этой причине в цифровой технике широкое распространение получила позиционная *овоичная* система счисления (с основанием 2). В каждом двоичном разряде, получившем название *бит*, может стоять 1 или 0. Сама же запись числа (двоичный код) представляет собой последовательность из единиц и нулей. Чтобы отличить двоичное число от десятичного, будем дополнять его справа суффиксом B (Binary), как это принято в специальных машинно-ориентированных языках программирования, называемых ассемблерами.

Веса соседних разрядов двоичного кода числа отличаются в два раза, а самый правый разряд (младший) имеет вес 1. Поэтому, например

$$101101B = 12^5 + 02^4 + 12^3 + 12^2 + 02^1 + 12^0 = 45.$$

Четыре соседних бита называют *темрадой*, группу из 8 бит называют *байтом*, а из 16 бит – *машинным словом*. Совокупность из  $1024~(2^{10})$  байт называют килобайтом, из 1024~ килобайт – мегабайтом, из 1024~ мегабайт – гигабайтом.

1 Гбайт =

$$2^{10}$$

Мбайт =  $2^{20}$  Кбайт =  $2^{30}$  байт.

Современные персональные ЭВМ могут хранить в своей памяти на жестких магнитных дисках цифровую информацию объемом в десятки гигабайт.

Арифметические операции в двоичной системе счисления исключительно просты и легко реализуются аппаратно. Однако при вводе и выводе информации в цифровое устройство она должна быть представлена в более привычной для человека десятичной системе счисления. Стремление упростить процедуру пересчета двоичных чисел к десятичному эквива-

ленту привело к использованию *двоично-десятичной системы счисления* (BD – Binary Decimals). Она используется в ЭВМ не только в качестве вспомогательной системы счисления при вводе и выводе данных, но и в качестве основной при решении задач, когда в ЭВМ вводится и выводится большое количество чисел, а вычислений над ними производится мало. Десятичные числа в двоично-десятичной системе счисления кодируются в прямом нормально-взвешенном коде 8-4-2-1, т.е. каждую цифру десятичного числа необходимо заменить соответствующей тетрадой двоичных чисел. Например, десятичное число 9531 в двоично-десятичном коде представляется машинным словом из четырех тетрад

$$9531 = 1001 \quad 0101 \quad 0011 \quad 0001.$$

Записывать двоичные числа большой разрядности утомительно. Поэтому, как правило, они представляются более компактными записями с использованием *шестнадцатеричной* системы счисления. В этой системе используют первые десять членов натурального ряда от 0 до 9, а в качестве остальных цифр — первые шесть латинских букв A = 10, B = 11, C = 12, D = 13, E = 14, F = 15. Справа шестнадцатеричное число будем дополнять суффиксом H (*Hexadecimal*).

Таблица 3.1 Соответствие чисел различных систем счисления

| Десятичное         | Шестиалиатерициое | Двоичное  |

|--------------------|-------------------|-----------|

| , ,                | Шестнадцатеричное | ' '       |

| число ( <i>D</i> ) | число (Н)         | число (В) |

| 0                  | 0                 | 0000      |

| 1                  | 1                 | 0001      |

| 2                  | 2                 | 0010      |

| 3                  | 3                 | 0011      |

| 4                  | 4                 | 0100      |

| 5                  | 5                 | 0101      |

| 6                  | 6                 | 0110      |

| 7                  | 7                 | 0111      |

| 8                  | 8                 | 1000      |

| 9                  | 9                 | 1001      |

| 10                 | A                 | 1010      |

| 11                 | В                 | 1011      |

| 12                 | C                 | 1100      |

| 13                 | D                 | 1101      |

| 14                 | E                 | 1110      |

| 15                 | F                 | 1111      |

Перевод двоичного числа в число системы с основанием 16 и наоборот не вызывает затруднений. Для этого исходное двоичное число справа налево разбивается на тетрады, а затем содержимое каждой из них рассматривается как двоичный код соответствующей цифры шестнадцатеричной системы. Для обратного перехода каждую цифру шестнадцатеричного числа заменяют тетрадой двоичного кода, например:

Для перевода целого числа  $N_p$ , представленного в системе счисления с основанием p, в систему счисления с основанием q необходимо данное число делить на основание q (по правилам системы с основанием p) до получения целого остатка, меньшего q. Полученное частное снова необходимо разделить на основание q и т.д., пока последнее частное не станет меньше q. Число  $N_q$  в новой системе счисления представится в виде упорядоченной последовательности остатков в порядке, обратном их получению. Причем цифру старшего разряда дает последнее частное.

**Пример 3.1.** Перевести десятичное число  $157_{10}$  в двоичный код, результат проверить.

| число         | делитель | остаток                                                             |

|---------------|----------|---------------------------------------------------------------------|

| <br>157       | 2        | 1 (младший разряд)                                                  |

| 78            | 2        | 0                                                                   |

| 39            | 2        | <u></u> 1                                                           |

| 19            | 2        | <u></u> 1                                                           |

| 9             | 2        | <del></del> 1                                                       |

| 4             | 2        | $ \begin{array}{ccc} \hline 0 & 157_{10} = 10011101_2 \end{array} $ |

| 2             | 2        | 0                                                                   |

| $\frac{1}{0}$ | 2        | 1 (старший разряд)                                                  |

Проверка:

$$100111101_2 = 1 \cdot 2^7 + 0 \cdot 2^6 + 0 \cdot 2^5 + 1 \cdot 2^4 + 1 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0 = 128 + 16 + 8 + 4 + 1 = 157_{10}$$

.

Для облегчения работы с двоичными кодами желательно знать наизусть десятичные значения чисел  $2^n$  от n=0 до n=14 (табл. 3.2).

Таблица 3.2

| n              | 0 | 1 | 2 | 3 | 4  | 5  | 6  | 7   | 8   | 9   | 10   | 11   | 12   | 13   | 14    |

|----------------|---|---|---|---|----|----|----|-----|-----|-----|------|------|------|------|-------|

| 2 <sup>n</sup> | 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | 256 | 512 | 1024 | 2048 | 4096 | 8192 | 16384 |

**Пример 3.2.** Перевести десятичное число  $157_{10}$  в восьмеричный код, результат проверить.

Проверка:  $235_8 = 2.8^2 + 3.8^1 + 5.8^0 = 128 + 24 + 5 = 157_{10}$ .

**Пример 3.3.** Перевести десятичное число  $157_{10}$  в шестнадцатеричный код, результат проверить.

|   | число | делитель | остаток                                        |

|---|-------|----------|------------------------------------------------|

| - | 157   | 16       | _13 (младший разряд)                           |

|   | 9     | 16       | $_{9}$ (старший разряд) $157_{10}$ = $9D_{16}$ |

|   | 0     |          |                                                |

Проверка:  $9D_{16} = 9.16^1 + 13.16^0 = 144 + 13 = 157_{10}$ .

С помощью байта данных можно представить различную информацию:

- целое число без знака (от 0 до 255);

- число от 0 до 99 в двоично-десятичном коде;

- машинный код команд микропроцессора;

- состояние восьми датчиков;

- двоичное число со знаком в прямом, обратном или *дополнительном* коде  $\pm X$ , где X модуль числа (от 0 до 127), для отображения которого используется семь младших разрядов. Старший разряд знаковый (0 для положительных чисел, 1 для отрицательных).

| Пример:            | +16           | -16                             |

|--------------------|---------------|---------------------------------|

| прямой код         | 0, X 00010000 | 1, <i>X</i> 10010000            |

| обратный код       | 0, X 00010000 | $1, \overline{X}$ 11101111      |

| дополнительный код | 0, X 00010000 | $1, \overline{X} + 1  11110000$ |

Прямой, обратный и дополнительный коды положительных чисел совпадают. Для получения дополнительного кода отрицательного числа можно проинвертировать код положительного числа и прибавить единицу. Дополнительный код однобайтового числа минус X равен дополнению до 256, т.е. двоичному коду числа 256-X. Преобразование дополнительного кода числа в прямой осуществляется по тому же правилу, что прямого в дополнительный.

**Пример 3.4.** Записать дополнительный код однобайтового числа минус 100. Для отображения знака используется старший разряд числа.

Решение. Запишем двоичный код числа плюс 100: 01100100

Проинвертируем его:

10011011

Прибавим единицу:

10011100

Проверка. 10011100=128+16+8+4=156=256-100.

Ответ: дополнительный код числа минус 100 равен 10011100В.

#### 3.2. Таблица истинности

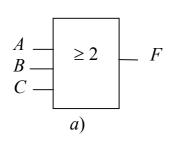

На рис. 3.1, a приведено функциональное обозначение цифрового устройства с тремя входами и одним выходом. Каждый из входных сигналов A, B и C может принимать лишь два значения: 1 и 0. Выходной сигнал F, который можно рассматривать как логическую функцию входных переменных A, B, C, на каждом их наборе F может быть равен 1 или F0.

| N | A | B | C | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 1 |

| 6 | 1 | 1 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 |

Рис. 3.1. Функциональное обозначение, таблица истинности и пример построения цифрового устройства

В простейшем случае функция F(A,B,C) может быть задана словесным описанием. Например, функция F равна 1, если все три ее переменные или любая пара из них равны 1, в противном случае F=0.

Любая логическая функция может быть задана в виде таблицы истинности. На рис. 3.1, 6 представлена таблица истинности для функции трех переменных, описанной выше словесно. Она определена на восьми наборах, которые располагаются в порядке нарастания десятичного эквивалента N их двоичного кода. В правом столбце указаны значения логической функции F на каждом наборе. Задание логической функции таблицей истинности не всегда удобно, так как при большом числе переменных она становится слишком громоздкой. В этом смысле наиболее привлекателен аналитический способ задания функций в виде так называемых структурных формул, показывающих, какие логические операции необходимо выполнить над входящими в них переменными, чтобы получить значения данной функции.

#### 3.3. Совершенная дизъюнктивная нормальная форма

По таблице истинности можно составить выражение для логической функции в **СДНФ** (совершенной дизъюнктивной нормальной форме), т.е. в виде суммы логических произведений, соответствующих единичным наборам функции:

$$F = \overline{ABC} + A\overline{BC} + AB\overline{C} + ABC. \tag{3.2}$$

Выражение (3.2) записано с использованием операций логического сложения (дизьюнкции), логического умножения (конъюнкции) и логического отрицания (инверсии), которые выполняют простейшие логические элементы ИЛИ, И и НЕ соответственно. Для каждого единичного набора составляется логическое произведение входных переменных, в которое переменная входит с инверсией при нулевом ее значении на данном наборе. Эти логические произведения объединяются затем знаком логического сложения (+ или ∨ ).

На рис. 3.2 представлены таблицы истинности и условные графические обозначения двухвходовых логических элементов. Кроме указанных выше, на практике широко используются элементы И-НЕ, ИЛИ-НЕ, Исключающее ИЛИ. Логическая функция последнего (функция «неравнозначность» или сумма по модулю два) в СДНФ записывается в виде  $A \oplus B = \overline{A}B + A\overline{B}$ .

Логические функции, представляющие собой *дизъюнкции* отдельных членов, каждый из которых есть некоторая функция, содержащая только конъюнкции, называют логическими функциями *дизъюнктивной нормальной формы* (ДНФ), например:  $F = XY + \overline{X}Z$ . Если же каждый член дизъюнкции нормальной формы от n аргументов содержит все эти аргументы, часть которых входит в него с инверсией, а часть – без нее, то такая

форма представления функции называется совершенной дизьюнктивной нормальной формой (СДНФ), например:  $F = \overline{ABC} + A\overline{BC} + AB\overline{C} + ABC$ .

Каждая конъюнкция этой дизъюнкции включает каждую переменную только один раз в прямом или инверсном виде, обращаясь в единицу при определенном наборе значений переменных, и носит название *минтерм*.

| Номер                 |         |   |                     |          |     |        |              |

|-----------------------|---------|---|---------------------|----------|-----|--------|--------------|

| набора                | A       | B | AB                  | AB       | A+B | A+B    | $A \oplus B$ |

| 0                     | 0       | 0 | 0                   | 1        | 0   | 1      | 0            |

| 1                     | 0       | 1 | 0                   | 1        | 1   | 0      | 1            |

| 2                     | 1       | 0 | 0                   | 1        | 1   | 0      | 1            |

| 3                     | 1       | 1 | 1                   | 0        | 1   | 0      | 0            |

|                       | Элемент | 1 | И                   | И-НЕ     | ИЛИ | ИЛИ-НЕ | Исключающее  |

|                       |         |   |                     |          |     |        | ИЛИ          |

| A                     | -       | П | -&-                 | -[&]_    | -1  | _1]    | <b>-</b> √=1 |

| $B \longrightarrow F$ |         |   | $ ^{\infty}$ $^{-}$ |          |     | '      |              |

|                       |         |   |                     | <u> </u> |     |        |              |

|                       |         |   | ЛИ                  | ЛА       | ЛЛ  | ЛЕ     | ЛП           |

|                       |         |   |                     |          |     |        |              |

Рис. 3.2. Таблицы истинности и условные графические обозначения двухвходовых логических элементов

Правило перехода от табличного задания логической функции к ее записи в СДНФ (правило записи логической функции по единицам) заключается в следующем:

- 1. Составить минтермы для строк таблицы истинности, на которых функция F равна 1. Если значение переменной в этой строке равно 0, то в минтерме записывается отрицание этой переменной.

- 2. Записать дизъюнкцию составленных минтермов, которая будет представлять переключательную функцию в СДНФ.

#### 3.4. Основные законы булевой алгебры

Математический аппарат, описывающий действия цифровых устройств, базируется на алгебре логики, автором которой считается английский математик Дж. Буль ( $1815-1864\ \Gamma$ .). В практических целях первым применил его американский ученый К. Шеннон в 1938 г. при исследовании электрических цепей с контактными выключателями.

В алгебре логики имеется четыре основных закона:

1. *Переместительный*, или закон *коммутативности* для операций сложения и умножения соответственно:

$$A+B = B+A;$$

$AB = BA.$

2. *Сочетательный*, или закон *ассоциативности* для сложения и умножения соответственно:

$$(A + B)+C = A+(B + C);$$

$(AB)C = A(BC).$

3. *Распределительный*, или закон *дистрибутивности* для сложения и умножения соответственно:

$$(A+B)C = AC + BC;$$

$(AB)+C = (A+C)(B+C).$

4. Закон *двойственности* или *инверсии* (*правило де Моргана*) сложения и умножения соответственно:

$$\overline{A + B} = \overline{A} \cdot \overline{B}; \qquad \overline{AB} = \overline{A} + \overline{B}.$$

Справедливость этих законов можно доказать с помощью таблиц истинности сложных логических связей, описываемых законом, или с помощью логических преобразований.

Для преобразований логических выражений пользуются легко доказываемыми тождествами, вытекающими из принципа работы простейших логических элементов (аксиомы алгебры Буля):

$$X+1=1;$$

$X\cdot 1=X;$   $X\oplus 1=\overline{X};$   $X+0=X;$   $X\cdot 0=0;$   $X\oplus 0=X;$   $X+X=X;$   $X\cdot X=X;$   $X\oplus X=0;$   $X+\overline{X}=1;$   $X\cdot \overline{X}=0;$   $X\oplus \overline{X}=1.$

С помощью законов алгебры логики и тождеств могут быть доказаны соотношения, получившие названия правил:

$$A + AB = A,$$

$$A \cdot (A + B) = A$$

и склеивания

$$A \cdot B + A \cdot \overline{B} = A,$$

$(A + B)(A + \overline{B}) = A.$

Эти правила широко используют для преобразования переключательных функций с целью их упрощения.

Из правила де Моргана вытекают следствия:

$$A + B = \overline{\overline{A} \cdot \overline{B}},$$

$$A \cdot B = \overline{\overline{A} + \overline{B}}.$$

с помощью которых появляется возможность выражать дизьюнкцию через коньюнкцию и отрицание, а коньюнкцию – через дизьюнкцию и отрицание. Законы двойственности справедливы для любого числа переменных.

В булевой алгебре при отсутствии в выражении скобок вводится следующий порядок действий: первыми выполняются операции отрицания, далее – конъюнкции, затем – дизъюнкции. Наличие в выражении скобок изменяет обычный порядок действий: в первую очередь должны выполняться операции внутри скобок.

Записанная ранее в СДНФ логическая функция трех переменных (3.2) может быть представлена в виде (ей соответствует схема устройства на рис. 3.1, 6):

$$F = C(\overline{AB} + A\overline{B}) + AB(\overline{C} + C) = C(A \oplus B) + AB$$

.

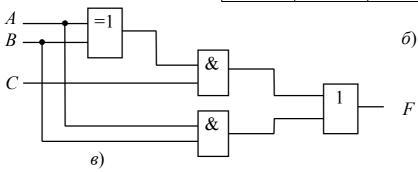

Набор логических элементов И, ИЛИ, НЕ называют *основным бази-сом* или основной функционально полной системой элементов. Последнее означает, что с помощью этих элементов можно реализовать устройство, осуществляющее сколь угодно сложную логическую операцию. Каждый из элементов И-НЕ и ИЛИ-НЕ также обладает функциональной полнотой.

Базисы И-НЕ и ИЛИ-НЕ называют *универсальными*. Эти базисы приобрели важное значение в связи с широким использованием интегральных логических элементов при построении логических устройств.

Структуры логических элементов НЕ, И, ИЛИ, построенных из элементов И-НЕ, приведены на рис. 3.3.

Схема отрицания НЕ реализована на использовании следующего со-

Рис. 3.3. Реализация схем: НЕ (а); И (б); ИЛИ (в)

отношения:  $y = \overline{x \cdot x} = \overline{x}$ .

Схема логического умножения использует принцип двойной инверсии:

$$y = \overline{x_1 x_2} = x_1 \cdot x_2.$$

Схема логического сложения двух сигналов базируется на использовании закона отрицания:

$$y = \bar{x}_1 \ \bar{x}_2 = x_1 \lor x_2.$$

Связующим звеном между реальным элементом и его переключательной функцией служит полярность логики. Различают положительную и отрицательную логику. При положительной логике в качестве логической единицы принят высокий уровень сигнала, при отрицательной логике – низкий уровень сигнала. Из принципа дуальности следует, что одно и то же логическое выражение может быть представлено двояко, например,

$$y = x_1 x_2 \quad u \quad y = x_1 \lor x_2.$$

Это значит, что один и тот же элемент будет реализовывать с точки зрения положительной логики функцию конъюнкции, а с точки зрения отрицательой логики – дизъюнкцию.

В дальнейшем в качестве единицы будет принят высокий уровень напряжения (положительная логика).

**Минимизация** — процесс приведения булевых функций к такому виду, который допускает наиболее простую, с наименьшим числом элементов, физическую реализацию функции. Частная задача минимизации булевой функции сводится к такому представлению заданной функции, которое содержит наименьшее возможное число букв и наименьшее возможное число операций над ними, так как каждой элементарной логической функции соответствует определенный физический элемент.

Оценить различные представления одной и той же булевой функции, например ДНФ, можно по количеству входов логических элементов, реализующих заданную функцию. Для минимизации переключательных функций применяют различные методы: последовательного исключения переменных с помощью законов алгебры логики, с использованием диаграмм Венна, карт Карно (Вейча) и др.

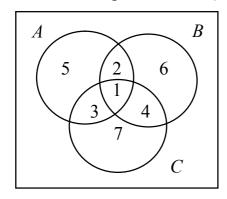

#### 3.5. Диаграммы Венна

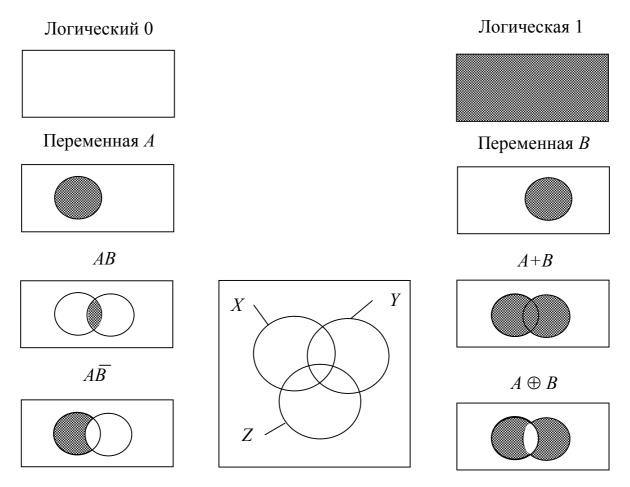

Логические функции можно отобразить на диаграммах Венна. Пусть левый круг (рис. 3.5) соответствует области прямых значений переменной A, правый — области прямых значений переменной B. Тогда область, образующаяся при пересечении кругов, соответствует логическому произведению AB. Область, образующаяся при наложении кругов, соответствует логической сумме A+B. Часть круга A, куда не входит B, соответствует логическому произведению  $A\overline{B}$ . Операции неравнозначности соответствует область, занимаемая двумя сегментами:  $A\overline{B}$  и  $\overline{AB}$ .

Рис. 3.5. Диаграммы Венна

С помощью диаграмм Венна легко доказывается справедливость логических тождеств. Для этого надо убедиться, что левой и правой частям записанных логических выражений соответствует одинаковое отображение на диаграмме Венна. Так, при наложении круга A и сегмента AB мы сохраняем отображение круга A, т.е. A+AB=A. При наложении отображения  $A \oplus B$  и сегмента AB получаем отображение логической суммы A+B, т.е.  $A \oplus B+AB=A+B$ . Если в области A+B исключить сегмент AB, то получим отображение операции «Исключающее ИЛИ», т.е.  $\overline{AB}(A+B)=A\oplus B$ .

Для доказательства тождества  $X\overline{Y}+\overline{X}Z=\overline{XY}(X+Z)$  удобно воспользоваться диаграммой Венна для логической функции трех переменных. Если в области X+Z исключить сегмент XY, получим отображение правой части выражения. Оно совпадает с отображением левой части, получаемым путем наложения сегментов  $X\overline{Y}+\overline{X}Z$ .

#### 3.6. Карты Карно

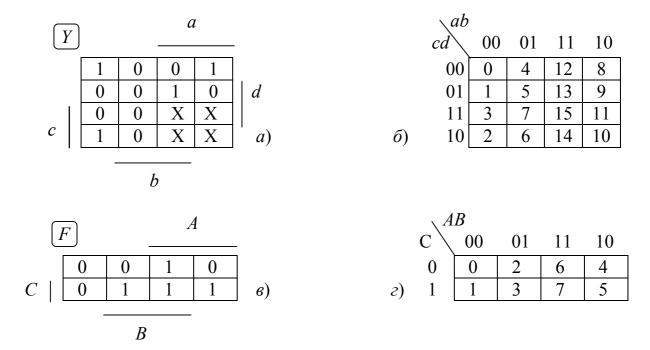

Для упрощения логических функций трех и четырех переменных удобно использовать карты Карно (рис. 3.6, a и 3.6, b). Карта Карно представляет собой прямоугольную таблицу, каждая клетка которой соответствует определенному набору таблицы истинности (рис. 3.6, b и 3.6, b). На карте фиксируют область прямых значений переменных и значение логической функции для каждого набора (0,1 или b), если функция на данном наборе не определена).

Карта Карно на рис. 3.6,  $\epsilon$  соответствует логической функции F, заданной выше словесно и с помощью таблицы истинности. Булева функция четырех переменных Y (рис. 3.6,  $\epsilon$ ) на четырех наборах принимает значение 1, на восьми наборах — 0, на четырех наборах — не определена (такие наборы иногда называют факультативными, они обозначены как  $\epsilon$ ).

Рис. 3.6. Карты Карно для логических функций трех (F) и четырех переменных (Y)

Карта Карно определяет значение функции на всех возможных наборах аргументов и, следовательно, является копией таблицы истинности. Карты Карно компактны и удобны для поиска склеиваемых членов переключательной функции СДНФ. Объясняется это тем, что два любых минтерма, находящихся в клетках, расположенных рядом друг с другом, явля-

ются соседними. Они могут быть заменены одной конъюнкцией, содержащей на одну переменную меньше. Группа из четырех минтермов, расположенных в соседних клетках, может быть заменена конъюнкцией, содержащей на две переменные меньше. В общем случае группа из  $2^k$  соседних клеток будет заменена одной конъюнкцией с n-k аргументами при общем числе переменных, равном n.

Правила записи минимизированного выражения для логической функции по карте Карно:

- 1) выделяются блоки (замкнутые прямоугольные области, содержащие 1, 2, 4, 8 клеток), заполненные единицами;

- 2) блоки должны быть возможно большими, а их количество наименьшим;

- 3) левая и правая, а также верхняя и нижняя строки карты считаются соседними;

- 4) блоки могут пересекаться, т.е. одна и та же клетка может входить в несколько блоков;

- 5) на факультативных наборах функция может доопределяться произвольно (на тех наборах, где стоят X), чтобы получить наиболее крупные блоки;

- 6) функция записывается в виде суммы логических произведений (ЛП), описывающих выделенные блоки;

- 7) переменная не включается в ЛП, если блок областью ее прямых значений делится пополам;

- 8) переменная включается в ЛП с инверсией, если рассматриваемый блок лежит в области ее инверсных значений;

- 9) при группировке в блоки клеток, заполненных нулями, по тем же правилам получаем инверсное значение логической функции.

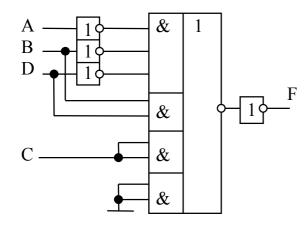

Логическая функция F (см. рис. 3.6) описывается совокупностью трех блоков (каждый блок включает группу из двух минтермов):

$$F = AB + BC + AC. (3.3)$$

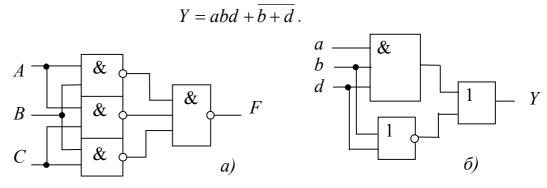

С использованием формулы двойственности ее можно преобразовать в вид, удобный для реализации в базисе И-НЕ (рис. 3.7, a):

$$F = \overline{AB} \cdot \overline{BC} \cdot \overline{AC}. \tag{3.4}$$

Логическая функция четырех переменных Y описывается совокупностью двух блоков (четыре угловые клетки считаются соседними):

$$Y = abd + \overline{b} \cdot \overline{d}$$

.

На рис. 3.7,  $\delta$  приведен пример ее реализации, учитывающий преобразование к виду

Рис. 3.7. Реализация логических функций F и Y

#### 3.7. Этапы синтеза цифрового устройства

При синтезе комбинационного цифрового устройства на логических элементах можно рекомендовать следующий порядок:

- 1) формируется словесное условие задачи (определяется, что именно должно делать разрабатываемое устройство, уточняется алгоритм его работы);

- 2) составляется таблица истинности для логической функции, реализуемой устройством, и записывается функция в СДНФ;

- 3) проводится минимизация логической функции с помощью карты Карно, диаграммы Венна или законов булевой алгебры;

- 4) функция преобразуется в вид, удобный для реализации на заданной элементной базе;

- 5) разрабатывается принципиальная схема цифрового устройства на логических элементах выбранной серии интегральных микросхем. Микросхемы логических элементов будут рассмотрены в следующей главе.

Результат синтеза не является однозначным, поэтому вариантов построения цифрового устройства может быть несколько. Следует стремиться к более простому решению поставленной задачи.

В следующем параграфе рассмотрены примеры синтеза комбинационных цифровых устройств на логических элементах ТТЛ (серия К155) и ТТЛШ (серия К555). При проектировании таких устройств надо четко представлять, каким образом формируются входные сигналы и как используются выходные сигналы.

#### 3.8. Примеры синтеза цифровых устройств

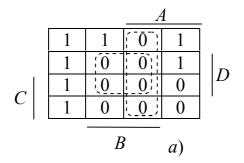

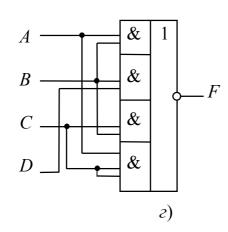

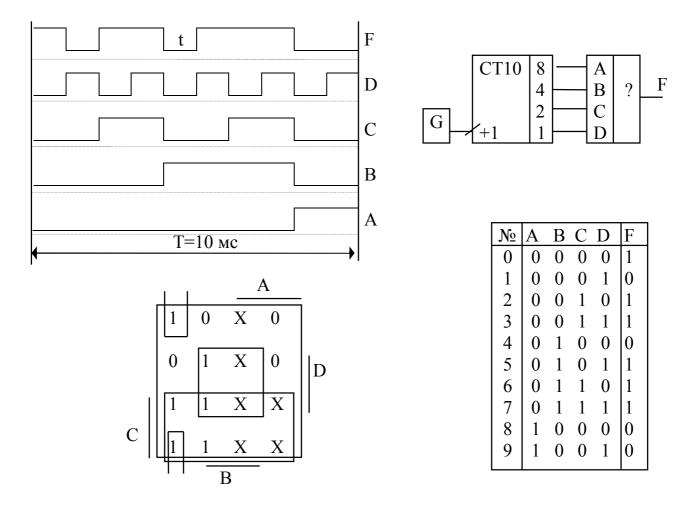

**Пример 3.5.** Реализовать устройство с четырьмя входами, логическая функция которого задана таблицей истинности (рис. 3.8,  $\theta$ ).

Pешение. Представим логическую функцию, реализуемую устройством, в виде соответствующей ей карты Карно (рис. 3.8, a). На рис. 3.8,  $\delta$  представлена таблица соответствия ее клеток наборам таблицы истинности.

| 0          | 4 | 12 | 8  |  |  |  |

|------------|---|----|----|--|--|--|

| 1          | 5 | 13 | 9  |  |  |  |

| 3          | 7 | 15 | 11 |  |  |  |

| 2          | 6 | 14 | 10 |  |  |  |

| <u>(i)</u> |   |    |    |  |  |  |

| n                                              | A                | В | C           | D                                    | F                          |

|------------------------------------------------|------------------|---|-------------|--------------------------------------|----------------------------|

| 0                                              | 0                | 0 | 0           | 0                                    | 1                          |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 0<br>0<br>0      | 0 | 0           | 1                                    | 1<br>1<br>1<br>1<br>0<br>0 |

| 2                                              | 0                | 0 | 1<br>1      | 0                                    | 1                          |

| 3                                              | 0                | 0 | 1           | 1                                    | 1                          |

| 4                                              | 0                | 1 | 0           | 0                                    | 1                          |

| 5                                              | 0<br>0<br>0<br>0 | 1 |             | 1                                    | 0                          |

| 6                                              | 0                | 1 | 1           | 0                                    | 0                          |

| 7                                              | 0                | 1 | 0<br>1<br>1 | 1                                    | 0                          |

| 8                                              | 1                | 0 | 0           | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | 0<br>1<br>1<br>0           |

| 9                                              | 1                | 0 | 0           | 1                                    | 1                          |

| 10                                             | 1                | 0 | 1<br>1      | 0<br>1                               | 0                          |

|                                                | 1                | 0 | 1           | 1                                    | 0                          |

| 12                                             | 1                | 1 | 0           | 0                                    | 0                          |

| 11<br>12<br>13<br>14                           | 1                | 1 | 0           | 1                                    | 0<br>0<br>0<br>0           |

| 14                                             | 1                | 1 | 1           | 1<br>0                               | 0                          |

| 15                                             | 1                | 1 | 1           | 1                                    | 0                          |

Рис. 3.8. Реализация устройства на микросхеме К555ЛРЗ в)

Организовав блоки по нулям (блоки AB и BD выделены на карте Карно пунктирной линией), запишем минимизированное выражение для логической функции по карте Карно:

$$\overline{F} = AB + BC + AC + BD$$

,

которое легко реализовать на микросхеме К555ЛР3 (рис. 3.8,  $\varepsilon$ ).

Если блоки организовать по единицам, то их число уменьшается до трех, но требуются дополнительные инверторы:

$$F = \overline{A} \cdot \overline{B} + \overline{B} \cdot \overline{C} + \overline{A} \cdot \overline{C} \cdot \overline{D}.$$

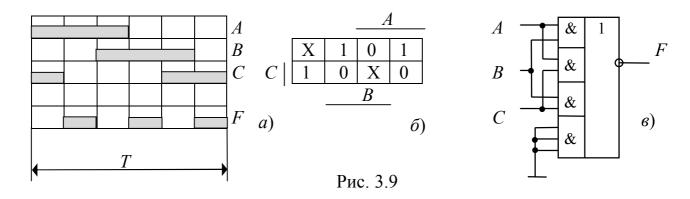

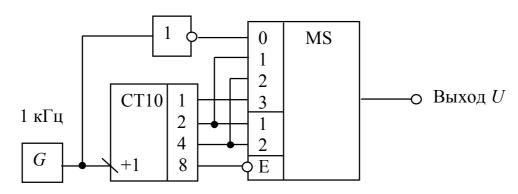

**Пример 3.6.** На микросхемах серии К155 спроектировать утроитель частоты напряжения трехфазной сети. Напряжение каждой фазы с помощью нуль-компараторов приведено к уровню ТТЛ (входной сигнал равен логической 1, когда синусоидальное напряжение фазы положительно).

Решение. Алгоритм работы устройства отображают временные диаграммы входных (A, B, C) и выходного (F) сигналов для одного периода T сетевого напряжения (рис. 3.9, a). Заполним карту Карно для единичных и нулевых тактов сигнала F (рис.  $3.9, \delta$ ). На двух наборах функция не определена (в трехфазной сети напряжения трех фаз не могут быть одновременно положительными или отрицательными). Организуя блоки по нулям, получаем

$$\overline{F} = AB + BC + AC$$

или  $F = \overline{AB + BC + AC}$ .

Наиболее просто эта функция реализуется на микросхеме  $K155 \Pi P3$  (рис. 3.9, в). Хотя бы на один из входов неиспользуемого элемента И надо подать логический 0, так как неподключенный вход  $TT\Pi$  ведет себя как вход с уровнем логической 1.

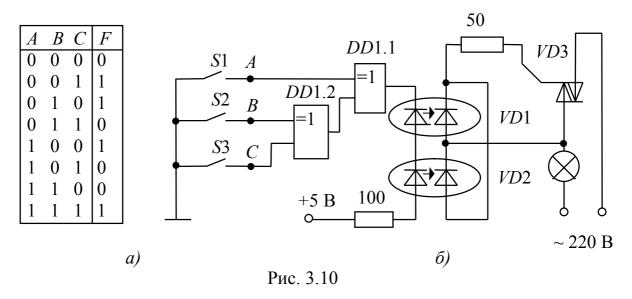

**Пример 3.7.** В трехэтажном доме лестничная клетка освещается одной общей лампочкой. На каждом этаже есть выключатели: S1, S2, S3. Спроектировать устройство включения и выключения освещения любым из выключателей, независимо от положения остальных.

Решение. Пусть A, B и C - сигналы на входе логической части устройства (замкнутому контакту выключателя соответствует уровень логического 0, а разомкнутому - уровень логической 1), F - сигнал на выходе логической части устройства (F=0, когда лампа горит). Заполним таблицу истинности, связывающую эти переменные (рис. 3.10, a). Запишем выходную функцию в СДНФ и попытаемся ее минимизировать, проводя простейшие преобразования полученной функции:

$$F = \overline{ABC} + \overline{ABC} + \overline{ABC} + ABC = \overline{A(BC + BC)} + A(\overline{BC} + BC)$$

или  $F = \overline{A(B \oplus C)} + A(\overline{B \oplus C}) = A \oplus B \oplus C$ .

Логическая часть устройства (рис. 3.10,  $\delta$ ) реализована на микросхеме DD1 (К155ЛП5). В корпусе этой микросхемы размещено четыре элемента "Исключающее ИЛИ". Последовательно с осветительной лампой включен симистор VD3 (ТС 122-25-4 или  $KY208\Gamma$ ), который управляется оптронными парами VD1, VD2 (AOY103A1). Ток через светодиоды пар выбран равным 10 мА (максимально допустимый ток в выходной цепи логического элемента в состоянии логического нуля -16 мА).

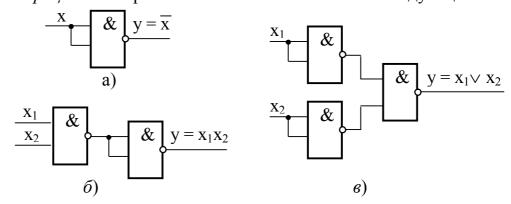

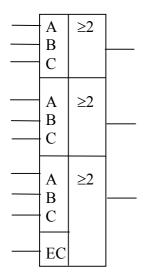

#### 3.9. Мажоритарный логический элемент

Идея мажоритарного резервирования — построение устройства, от которого требуется высокая надежность, в виде трех идентичных устройств, выходные сигналы которых объединяются с помощью мажоритарных элементов. В этом случае выход из строя одного из устройств не

Рис. 3.11. Микросхема КР1533ЛП3

приведет к появлению неправильных сигналов на выходе мажоритарного элемента, так как они будут определяться сигналами двух исправных устройств. Если каждое из устройств разбить на несколько блоков, между которыми встроить мажоритарные элементы, можно еще более повысить надежность устройства в целом. Для систем мажоритарного резерспециально разработана вирования микросхема КР1533ЛП3 (рис. 3.11), которая содержит три мажоритарных элемента, имеющих дополнительный вход управления EC. При EC=0 выходной сигнал каждого элемента равен 1 в случае, если не менее, чем на двух из трех входов A, B, C действует единичный сигнал. При EC=1 на выход проходит сигнал со входа C независимо от сигналов на других входах.

### 4. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

### 4.1. Классификация логических элементов

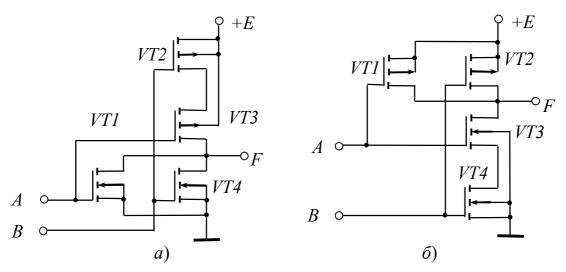

Для современной схемотехники характерно широкое использование базисов И-НЕ и ИЛИ-НЕ. Для их реализации логические элементы строят, как правило, из двух частей: части схемы, выполняющей операции И или ИЛИ (так называемой входной логики), и инвертора, выполняющего операцию НЕ. Входная логика может быть выполнена на различных полупроводниковых элементах: диодах, биполярных и полевых транзисторах. В зависимости от вида полупроводниковых элементов, применяемых для изготовления входной логики и инверторов, различают:

- ДТЛ диодно-транзисторную логику;

- ТТЛ транзисторно-транзисторную логику;

- ТТЛШ ТТЛ с диодами Шоттки;

- ЭСЛ эмиттерно-связанную логику;

- $\text{И}^2 \text{Л}$  интегральную инжекционную логику;

- КМОП логику на комплементарных парах полевых транзисторов;

- ИСЛ (GaAs) истоково-связанную логику с управляющим затвором Шоттки.

В следующих параграфах будет рассмотрено устройство и работа базовых элементов ТТЛ, ТТЛШ, ЭСЛ и КМОП, как имеющих в настоящее время наиболее широкое применение.

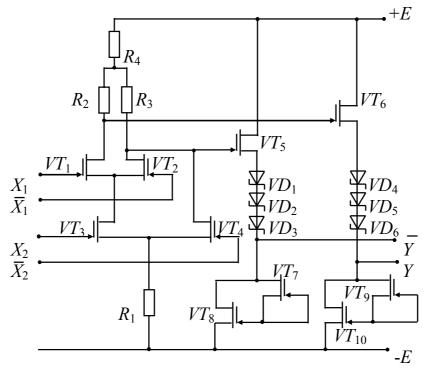

### 4.2. Базовый элемент ТТЛ

Транзисторно-транзисторная логика (ТТЛ) малой степени интеграции появилась на первом этапе развития интегральной схемотехники (1969 – 1985 гг.). Эти схемы характеризуются хорошими электрическими параметрами, удобны в применении, обладают большим функциональным разнообразием. Отечественная промышленность выпускала микромощную серию 134 и стандартные серии 133, 155 (аналоги зарубежных SN54, SN74).

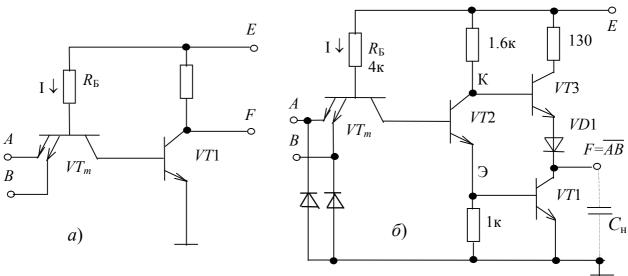

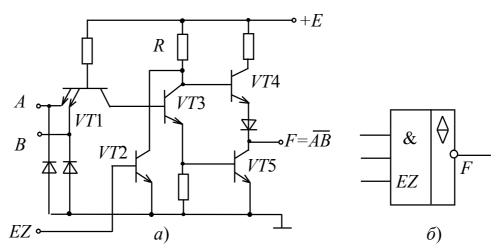

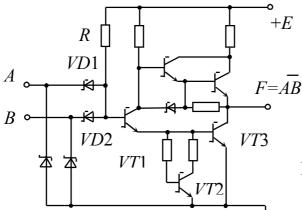

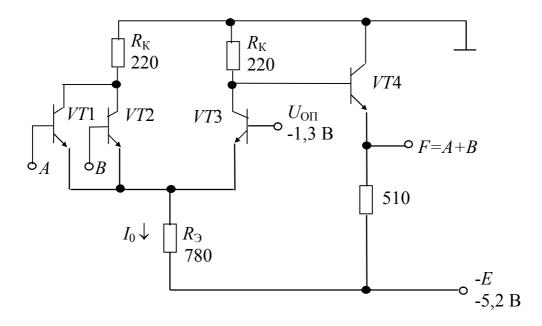

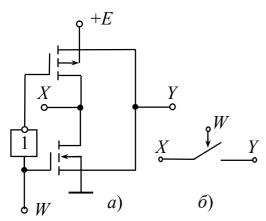

Простейший логический элемент ТТЛ строится на базе многоэмиттерного транзистора  $VT_m$ , выполняющего функцию И для сигналов, подаваемых на его эмиттеры, и транзисторного ключа VT1, выполняющего функцию НЕ (рис. 4.1, a). Если на всех входах высокие уровни напряжения (A=1 и B=1), закрыты эмиттерные переходы  $VT_m$ , открывается переход база-коллектор этого транзистора и ток I открывает и насыщает ключевой транзистор VT1, формируя на выходе низкий уровень напряжения (F=0). При низком уровне сигнала на любом из входов ток I переключается в выходную цепь источника сигнала, закрывая VT1. При этом F=1. Таким образом, схема реализует таблицу истинности элемента 2И-НЕ.

Рис. 4.1. Базовая схема элемента ТТЛ

Для повышения экономичности и быстродействия выходной ключ выполняют по схеме сложного инвертора (рис. 4.1,  $\delta$ ). При A=B=1 открыты транзисторы VT2, VT1 (транзистор VT3 закрыт) и емкость нагрузки  $C_{\rm H}$  быстро разряжается через сопротивление открытого ключа VT1. Для любой другой комбинации входных сигналов емкость нагрузки имеет возможность быстро зарядиться до высокого уровня напряжения через низкое выходное сопротивление эмиттерного повторителя VT3 (VT2 и VT1 закрыты).

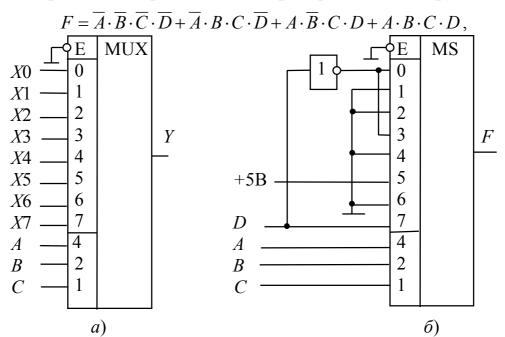

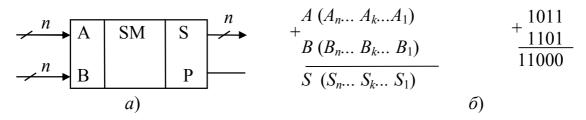

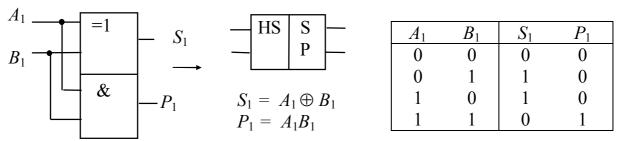

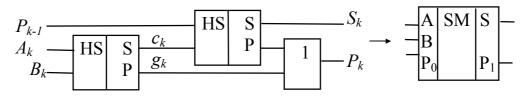

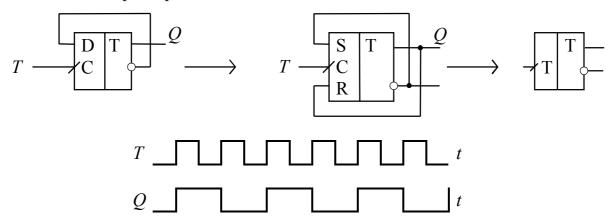

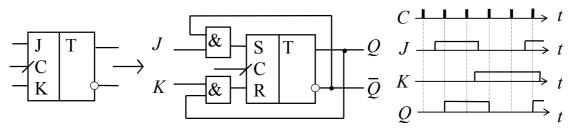

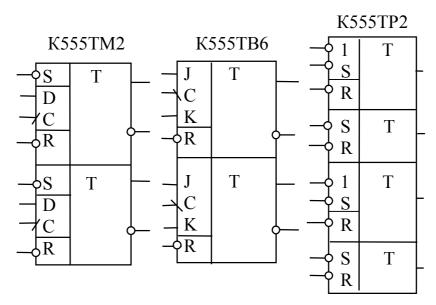

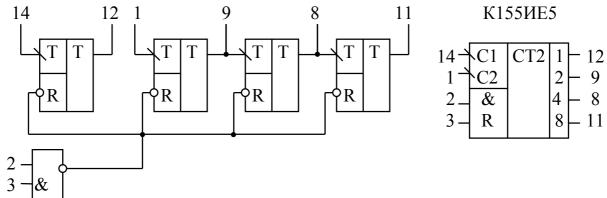

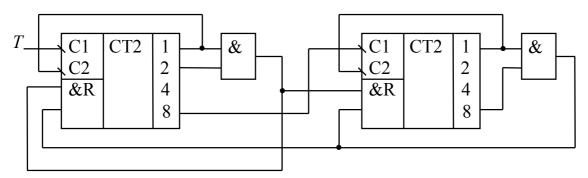

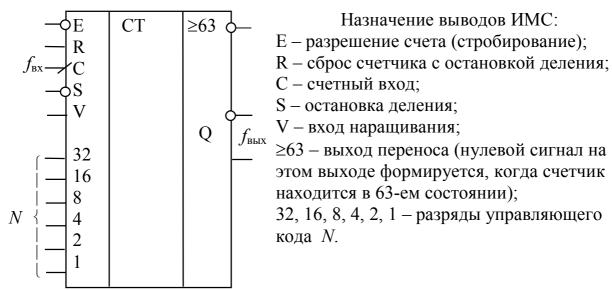

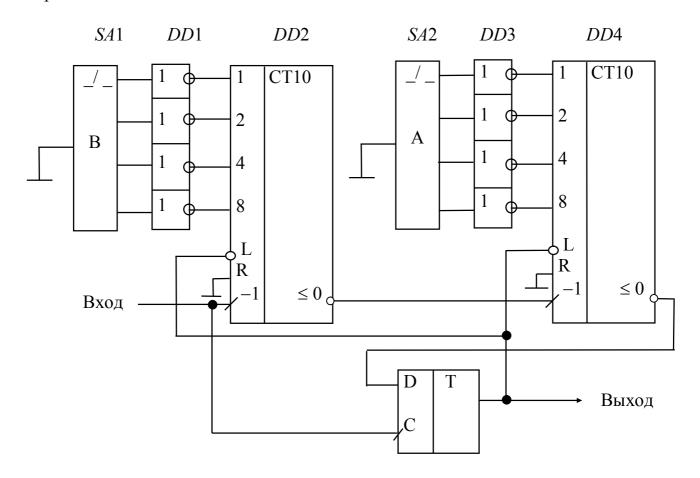

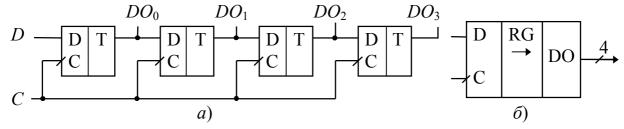

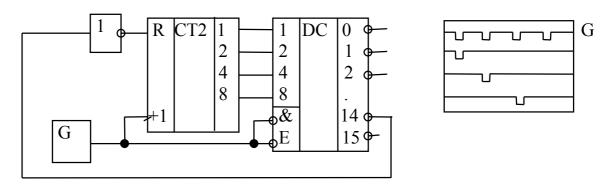

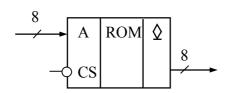

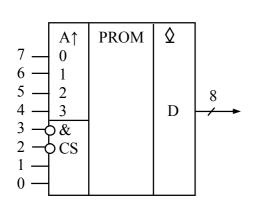

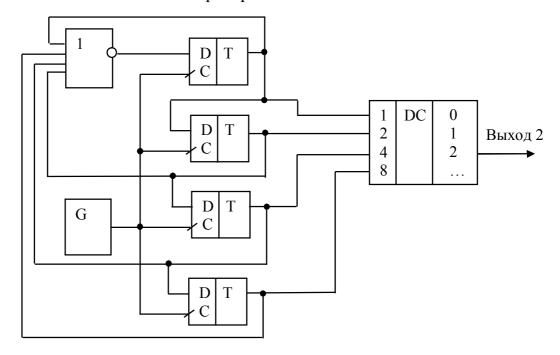

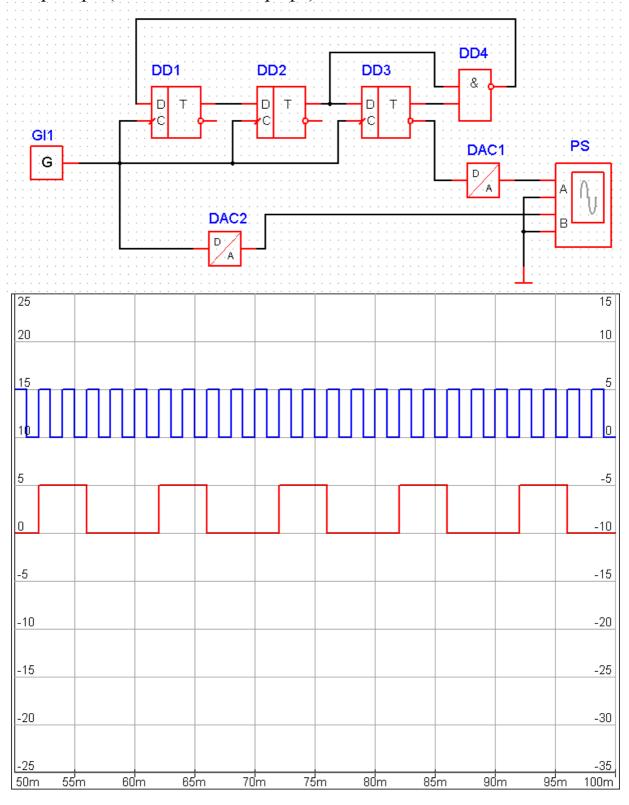

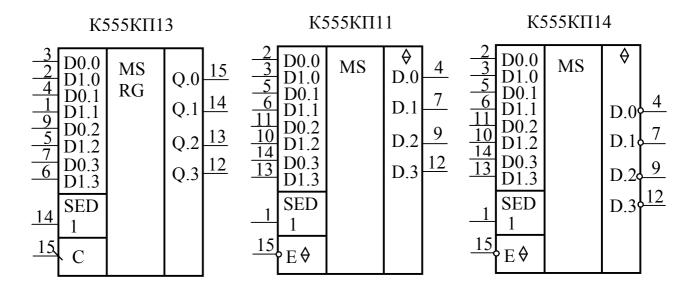

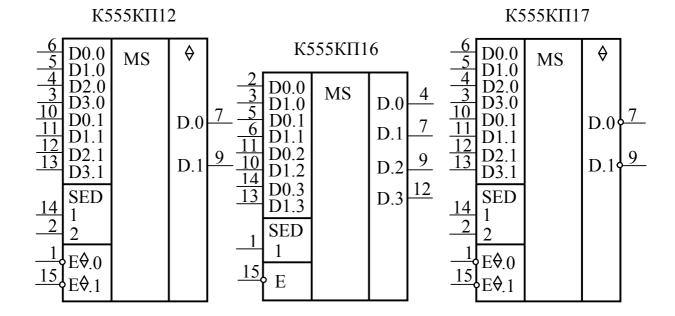

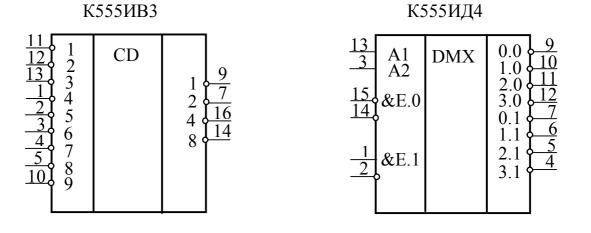

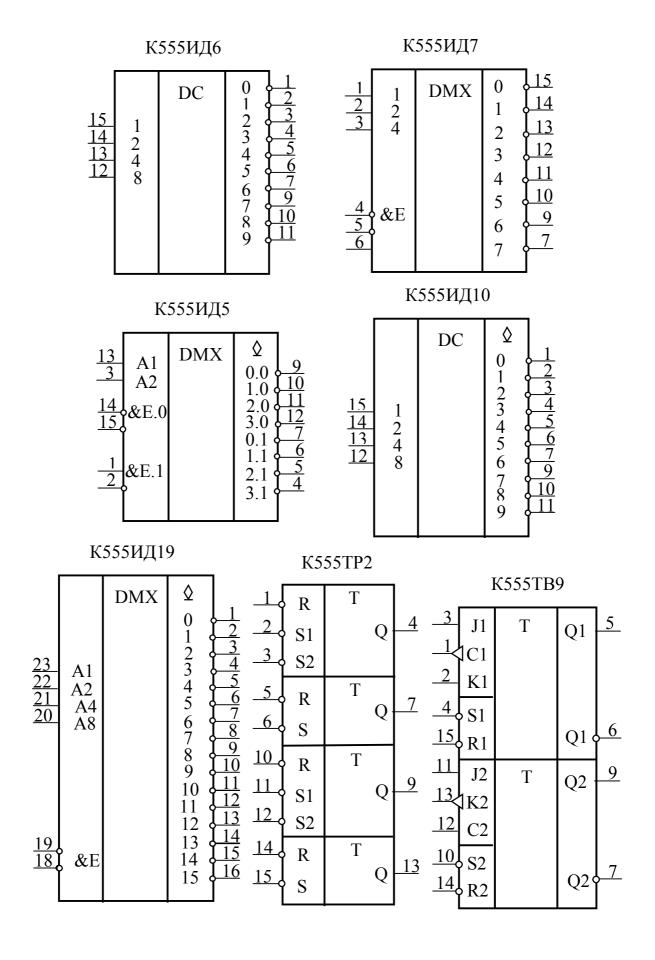

Собственное потребление тока в выходной цепи отсутствует как при логическом нуле на выходе (закрыт VT3), так и при логической 1 на выходе (закрыт VT1). В этом отношении сложный инвертор на биполярных транзисторах подобен инвертору на КМОП-транзисторах.